# UNIVERSITY OF CALIFORNIA, IRVINE

### System Level Modeling of an AMBA Bus

**THESIS**

submitted in partial satisfaction of the requirements for the degree of

MASTER OF SCIENCE

in Electrical and Computer Engineering

by

Hans Gunar Schirner

Thesis Committee: Professor Rainer Dömer , Chair Professor Daniel D. Gajski Professor Pai H. Chou

| The thesis of Hans Gun  | ar Schirner is approved: |                 |

|-------------------------|--------------------------|-----------------|

| The thesis of Hans Gain | ar semmer is approved.   |                 |

|                         |                          |                 |

|                         |                          |                 |

|                         |                          |                 |

|                         |                          |                 |

|                         |                          |                 |

|                         |                          |                 |

|                         |                          |                 |

|                         |                          |                 |

|                         |                          |                 |

|                         |                          | Committee Chair |

University of California, Irvine 2005

To my family.

# **Contents**

| Li | st of l | Figures                                                          | vi   |

|----|---------|------------------------------------------------------------------|------|

| Li | st of ' | Tables                                                           | viii |

| Li | st of A | Acronyms                                                         | ix   |

| A  | cknow   | vledgments                                                       | xi   |

| A  | bstrac  | et of the Thesis                                                 | xii  |

| 1  | Intr    | oduction                                                         | 1    |

|    | 1.1     | Introduction to SoC Design                                       | 1    |

|    |         | 1.1.1 Overview                                                   | 1    |

|    |         | 1.1.2 Challenges                                                 | 1    |

|    |         | 1.1.3 SoC Specification                                          | 2    |

|    |         | 1.1.4 SoC Design Space Exploration                               | 3    |

|    | 1.2     | Problem Definition                                               | 5    |

|    | 1.3     | Thesis Overview                                                  | 6    |

|    | 1.4     | Related Work                                                     | 6    |

| 2  | Intr    | oduction to the AMBA Bus                                         | 8    |

| 3  | Mod     | leling                                                           | 11   |

|    | 3.1     | Layering                                                         | 11   |

|    | 3.2     | Graphical Notation                                               | 16   |

|    | 3.3     | Transaction Level Model - MAC                                    | 16   |

|    | 3.4     | Arbitrated Transaction Level Model - Protocol                    | 17   |

|    | 3.5     | Bus Functional Model - Physical                                  | 19   |

|    | 3.6     | Modes of Access                                                  | 22   |

| 4  | Vali    | dation                                                           | 23   |

|    | 4.1     | Functional Validation                                            | 23   |

|    |         | 4.1.1 Validation of Individual Bus Transfers – Fundamental Tests | 23   |

|    |         | 4.1.2 Validation of the Memory Interface                         | 25   |

|          |        | 4.1.3 Validation of the Rendezvous Interface                                     | 26 |

|----------|--------|----------------------------------------------------------------------------------|----|

|          | 4.2    | Timing Validation of the Bus Functional Model                                    | 27 |

|          |        | 4.2.1 Basic Pipelined Bus Access                                                 | 28 |

|          |        | 4.2.2 Error Response                                                             | 29 |

|          |        | 4.2.3 Unlocked Burst Handover                                                    | 31 |

|          |        | 4.2.4 Locked Burst Handover                                                      | 33 |

|          |        | 4.2.5 Locked Burst Handover with Master Busy                                     | 34 |

|          |        | 4.2.6 Retry                                                                      | 36 |

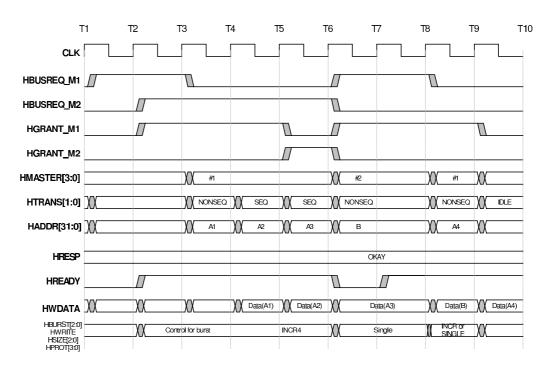

|          |        | 4.2.7 Preemption of an Unlocked Burst                                            | 37 |

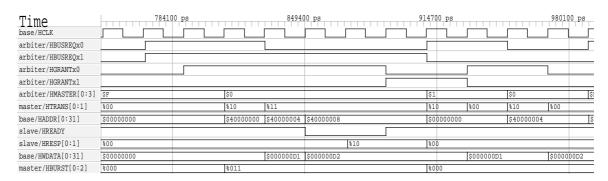

|          | 4.3    | Timing Validation of the Transaction Level Models                                | 40 |

|          | 4.4    | Validation Summary                                                               | 42 |

| 5        | Mod    | lel Analysis                                                                     | 43 |

|          | 5.1    | Performance Analysis                                                             | 43 |

|          |        | 5.1.1 Test Setup                                                                 | 43 |

|          |        | 5.1.2 Simulation Time                                                            | 44 |

|          |        | 5.1.3 Simulated Bandwidth                                                        | 45 |

|          | 5.2    | Accuracy Analysis                                                                | 46 |

|          |        | 5.2.1 Test Setup                                                                 | 47 |

|          |        | 5.2.2 Accuracy of Locked Transfers                                               | 48 |

|          |        | 5.2.3 Accuracy of Unlocked Transfers                                             | 52 |

|          | 5.3    | Analysis Summary                                                                 | 54 |

| 6        | Sum    | mary and Conclusions                                                             | 56 |

| Bi       | bliogr | raphy                                                                            | 58 |

| ٨        | Наза   | der Files                                                                        | 61 |

| <b>7</b> | A.1    | <i>i_ambaAHBbus.sh</i> : MAC Layer Interface Definitions for Master and Slave    | 62 |

|          |        | ambaAHBbusMaster.sc: Bus Functional Interfaces and Channel Definition for Master | -  |

|          | A.3    | ambaAHBbusSlave.sc: Bus Functional Interfaces and Channel Definition for Slave   | 64 |

|          | A.4    | ambaAHBbusTLM.sc: Interfaces and Channel Definitions for Abstract Models         | 66 |

| _        | -      |                                                                                  |    |

| В        |        | ing Environment                                                                  | 68 |

|          | B.1    | Source Code Structure                                                            | 68 |

|          | B.2    | Test Executables                                                                 | 70 |

# **List of Figures**

| 1.1<br>1.2<br>1.3 | Abstraction levels in SoC design                                               | 3  |

|-------------------|--------------------------------------------------------------------------------|----|

| 2.1<br>2.2        | AMBA hierarchical bus architecture                                             | 10 |

| 3.1               | Decomposition of a user transaction                                            | 15 |

| 3.2               | Graphical notation for model description                                       | 16 |

| 3.3               | Transaction Level Model (MAC model) connection scheme                          | 17 |

| 3.4               | Arbitrated Transaction Level Model (protocol model) connection scheme          | 18 |

| 3.5               | Bus functional model connection scheme                                         | 19 |

| 3.6               | Content of the bus functional channel                                          | 20 |

| 3.7               | Channels for master bus functional model                                       | 21 |

| 3.8               | Channels for slave bus functional model                                        | 21 |

| 3.9               | Modes of access                                                                | 22 |

| 4.1               | Logical connection for individual bus transfer validation                      | 24 |

| 4.2               | User level logical connection for memory and rendezvous type access validation | 26 |

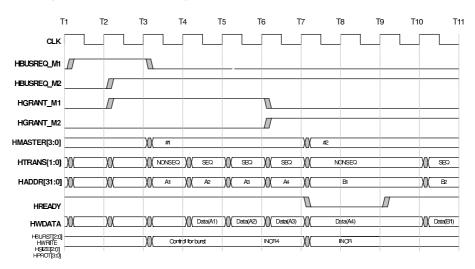

| 4.3               | Reference sequence showing pipelined behavior                                  | 28 |

| 4.4               | Waveform of implemented bus model, showing pipelined behavior                  | 28 |

| 4.5               | Reference sequence showing an error response                                   | 30 |

| 4.6               | Waveform of implemented bus model, showing error response                      | 30 |

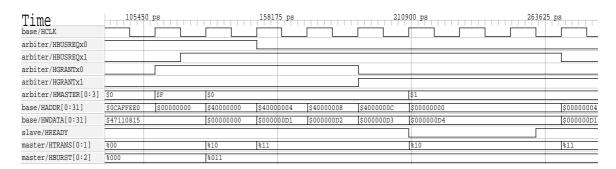

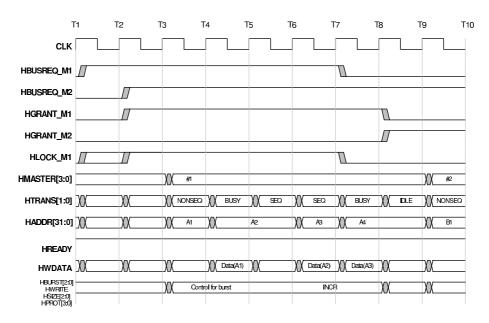

| 4.7               | Reference showing unlocked burst handover                                      | 31 |

| 4.8               | Waveform of implemented bus model, unlocked burst handover                     | 31 |

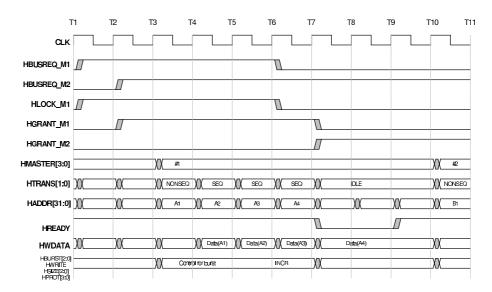

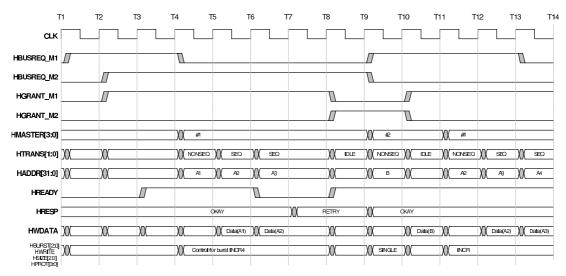

| 4.9               | Reference sequence, locked burst handover                                      | 34 |

| 4.10              | Waveform of implemented bus model, locked burst handover                       | 34 |

| 4.11              | Reference sequence showing a locked burst with busy cycle                      | 35 |

| 4.12              | Waveform of implemented bus model, showing locked transfer with busy master    | 35 |

| 4.13              | Reference sequence showing an aborted burst due to retry                       | 37 |

| 4.14              | Waveform of implemented bus model, showing a retry                             | 37 |

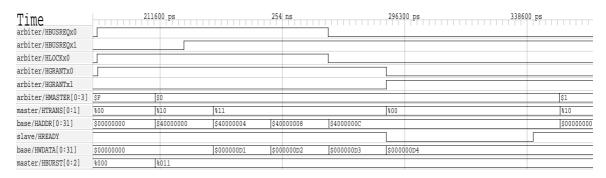

| 4.15              | Reference sequence showing soss of bus grant during burst                      | 39 |

| 4 16              | Waveform of implemented bus model showing soss of bus grant during burst       | 30 |

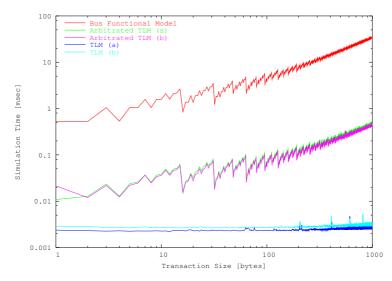

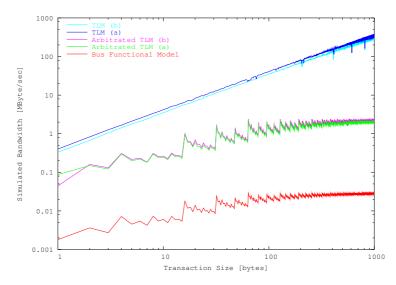

| 5.1 | Execution time of implemented models                         | 45 |

|-----|--------------------------------------------------------------|----|

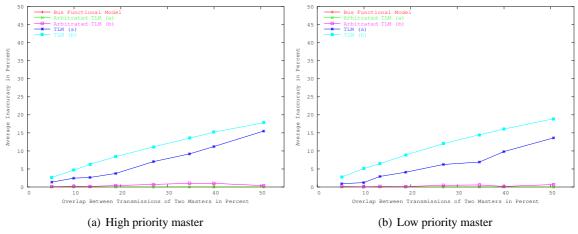

| 5.2 | Simulated bandwidth                                          | 46 |

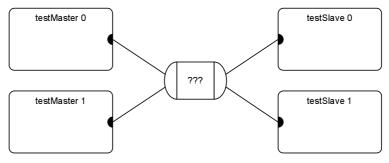

| 5.3 | Logical connection scheme for accuracy tests                 | 47 |

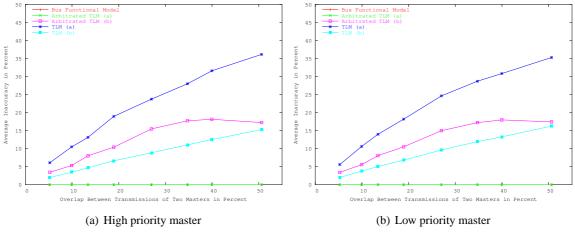

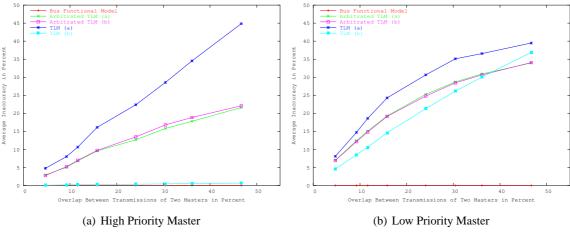

| 5.4 | Locked transfer accuracy based on duration                   | 49 |

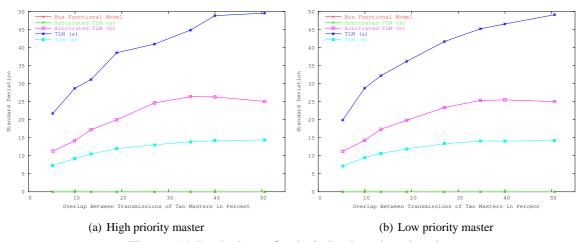

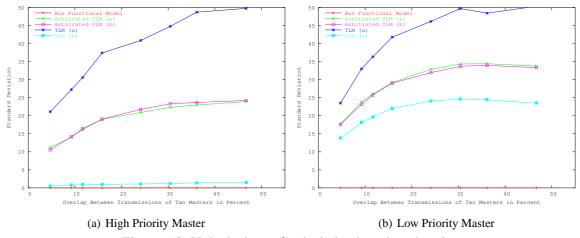

| 5.5 | Locked transfer deviation based on duration                  | 50 |

| 5.6 | Locked transfer accuracy based on cumulative transfer time   | 51 |

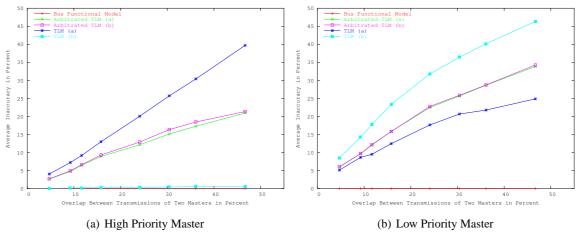

| 5.7 | Unlocked transfer accuracy based on duration                 | 52 |

| 5.8 | Unlocked transfer deviation based on duration                | 53 |

| 5.9 | Unlocked transfer accuracy based on cumulative transfer time | 54 |

| B.1 | Generic connection scheme                                    | 68 |

# **List of Tables**

| 3.1 | Communication layers                                              | 12 |

|-----|-------------------------------------------------------------------|----|

| 3.2 | Implemented layers and their granularity of data handling         | 14 |

| 4.1 | Results of individual bus transfer validation                     | 24 |

| 4.2 | Results of validation for memory access                           | 26 |

| 4.3 | Results of functional verification of rendezvous access           | 27 |

| 4.4 | Testcase definition for individual bus transfer timing validation | 41 |

| 4.5 | Results of individual bus transfer timing validation              | 41 |

| 6.1 | Conclusion summary                                                | 56 |

| B.1 | Implemented test files                                            | 69 |

|     | Implemented bus models                                            |    |

| B.3 | Generated graphics for timing accuracy                            | 71 |

# **List of Acronyms**

- **AHB** Advanced High-performance Bus. System bus definition within the AMBA 2.0 specification. Defines a high-performance bus including pipelined access, bursts, split and retry operations.

- **AMBA** Advanced Microprocessor Bus Architecture. Bus system defined by ARM Technologies for system-on-chip architectures.

- **APB** Advanced Peripheral Bus. Peripheral bus definition within the AMBA 2.0 specification. The bus is used for low power peripheral devices, with a simple interface logic.

- **ASB** Advanced System Bus. System bus definition within the AMBA 2.0 specification. Defines a high-performance bus including pipelined access and bursts.

- **ATLM** Arbitrated Transaction Level Model. A model of a system in which communication is described as transactions, abstract of pins and wires. In addition to what is provided by the TLM, it models arbitration on a bus transaction level.

- **Behavior** An encapsulating entity, which describes computation and functionality in the form of an algorithm.

- Bus Functional Model A wire accurate and cycle accurate model of a bus.

- **Channel** An encapsulating entity, which abstractly describes communication between two or more partners.

- **CLI** Cycle Level Interface. Refers to ARMs definition of the AMBA bus, cycle level accurate for SystemC.

- IP Intellectual Property. A pre-designed system component.

- MAC Media Access Control. Layer within the OSI layering scheme.

- NoC Network on Chip

- **OS** Operating System. Software entity that manages and controls access to the hardware of a computer system. It usually provides scheduling, synchronization and communication primitives.

- **OSI** Open Systems Interconnection. An communication architecture model, described in seven layers, developed by the ISO for the interconnection of data communication systems.

- **PE** Processing Element. A system component that provides computation capabilities, e.g. a custom hardware or generic processor.

- **RTL** Register Transfer Level. Description of hardware at the level of digital data paths, the data transfer and its storage.

- **RTOS** Real-Time Operating System. An operating system that responds to an external event within a short, predictable time.

- **SCE** SoC Environment. A set of tools for the automated, computer-aided design of SoC and computer systems.

- **SoC** System-On-Chip. A highly integrated device implementing a complete computer system on a single chip.

- **TLM** Transaction Level Model. A model of a system in which communication is described as transactions, abstract of pins and wires.

# **Acknowledgments**

Here I wish to thank those who have supported me during the process of the thesis work. First and foremost I want to thank my advisor Rainer Dömer, for the guidance and the support he as given me throughout the work. Especially I appreciate our constructive discussions, which helped in identifying and solving problems.

Furthermore I want to thank Prof. Daniel Gajski for serving on my committee. His critical, yet visionary comments and discussions are definitely an enrichment for the work and the work environment. In addition, I would also like to thank Prof. Pai Chou for serving on my committee and for his valuable comments on improving this thesis.

This thesis work was also influenced by the members of the SpecC/SCE group, through discussions and meetings. The people are who make the CECS an excellent research place. In particular I would like to thank Andreas Gerstlauer for his contribution of ideas and patience in discussions.

### **Abstract of the Thesis**

System Level Modeling of an AMBA Bus

by

Hans Gunar Schirner

Master of Science in Electrical and Computer Engineering

University of California, Irvine, 2005

Professor Rainer Dömer, Chair

The System-On-Chip (SoC) design faces a gap between the production capabilities and time to market pressures. The design space, to be explored during the SoC design, grows with the improvements in the production capabilities and it takes an increasing amount of time to design a system that utilizes those capabilities. On the other hand shorter product life cycles are forcing an aggressive reduction of the time-to-market. Addressing this gap has been the aim of recent research work. As one approach abstract models have been introduced and a design flow was devised that guides the designer in the process from a most abstract model down to a synthesizable model.

Throughout the design process computation and communication concerns are handled individually. The communication is mostly abstracted away from the designer, which allows the design focus to rest on the application specific computation. This separation requires the provider of an SoC design tool to supply fast and accurate communication models.

Fast simulation capabilities are required for coping with the immense design space that is to be explored; these are especially needed during early stages of the design. This need has pushed the development of transaction level models, which are abstract models that execute dramatically faster than synthesizable models. The pressure for fast executing models extends especially to the frequently used and reused communication libraries. This thesis describes the system level modeling of the Advanced High-performance Bus (AHB) part of the Advanced Microprocessor Bus Architecture (AMBA). Throughout this work the design of three bus models, at different levels of abstraction, is described; their simulation speed and accuracy is evaluated. As a result guidelines for the developer are derived that support selecting the most appropriate model for a given stage in the design process.

## **Chapter 1**

### Introduction

### 1.1 Introduction to SoC Design

#### 1.1.1 Overview

Improvements in manufacturing capabilities allow placing of a complete embedded system on a single chip. With that it becomes possible to design a system as a mix of software running on one or more generic processors and specialized hardware, which runs computation that is too costly for a generic processor (e.g. in terms of power or time). This design freedom leads ultimately to highly specialized chips and cost efficient production. However the newly gained freedom in design places a burden on the SoC designer. The next paragraphs will introduce the challenges of system level design, the specification of systems and the design space exploration.

#### 1.1.2 Challenges

The design of embedded systems in general and an SoC in special will be done under functional and environmental constraints. Since the designed system will run under a well-specified operating environment, the strict functional requirements can be concretely defined. The environment restrictions on the other hand are more diverse: e.g. minimizing the cost, footprint, or power consumption. Due to the flexibility of a SoC design, achieving the set goals, involves analyzing a multi-dimensional design space. The degrees of freedom stem from the process element types and characteristics, their allocation, the mapping of functional elements to the process elements, their interconnection with busses and their scheduling.

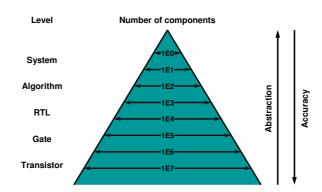

Figure 1.1: Abstraction levels in SoC design (source [12])

Looking at the levels of abstraction of the SoC design gives another perspective to the complexity of designing such systems. The process starts with a functional description on system level, where only the major function blocks are defined and timing information is not yet captured. During the SoC design process, the system description is refined step by step and additional details are captured. That process leads to a cycle accurate fully functional system description in RTL, which is the starting point of the production process. As Figure 1.1 shows, the amount of captured information increases by an oder of magnitude with each level of the design process. With each step within the levels of abstraction a multi-dimensional design space has to be explored in order to make the necessary decisions.

The goal of SoC design paradigm is to guide the designer through the process, and aid the decision making. A well-defined flow of design steps makes the process manageable. The design steps and their associated models will be described in the next paragraphs.

#### 1.1.3 SoC Specification

Hardware/Software co-design is an integral aspect of the SoC design. It requires a language that is capable of capturing the requirements of a hardware design from wire allocations to complex timing requirements, as well as the complexities of current software design. Some examples of such languages are SpecC [10], an ANSI-C based language extension and the C++ library extension SystemC [14].

Those languages allow grouping of functionality to behaviors, which later can be freely mapped to processing elements. In order to allow this free mapping the computation has to be separated from the communication. Therefore communication between the behaviors is abstractly defined as channels. The channel specific implementation (e.g. an AMBA protocol) will be filled

in during later refinement stages. The specification model is free of such implementation detail (and their respective constraints). The SpecC language further introduces many concepts from hardware description languages like VHDL and Verilog. It introduces the concept of capturing scheduling information in the language, such as sequential, parallel and pipelined execution. The SpecC language very much supports the goals of specification capturing. It allows describing a fully functional model that incorporates design constraints and has a simulation environment for an integrated validation against a set of test vectors. The next section describes the exploration and refinement steps to transform the system specification into a manufacturable description.

#### 1.1.4 SoC Design Space Exploration

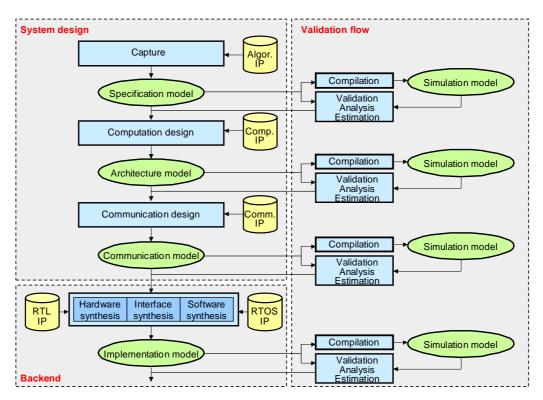

In conjunction with the SpecC language a design paradigm was introduced, which formalizes the individual refinements steps. With that the designer has guidelines on how to efficiently handle the immense design space. Figure 1.2 shows an overview of the design flow. It also indicates the integration of the validation flow. The tool suite provided with the SpecC language closely follows the outlined design flow. The following paragraphs will describe each design step.

Figure 1.2: Design methodology for SoC design (Source [11])

The SoC design starts with the specification model, which is a purely functional model - free of any implementation details. It focuses on capturing the algorithmic behavior and allows a functional validation of the description. The model is untimed and allows only for causal ordering. Once the specification model is finished, it will serve as a golden model, to compare simulation results during the design cycle.

Architecture information is added during the Computation design. During this step processing elements are inserted into the system and the previously defined functional behaviors are mapped to them. A processing element can be a predefined standard component such as generic processor core or a DSP, but a custom specific hardware component as well. Parameters, such as clock frequency, of the inserted elements can be adjusted to the application needs. Based on internal statistics, early estimations about the runtime performance can be made. This gives the designer the first feedback about the design decisions. Once the computation design is finished, the architecture model that captures the decisions is created. This model is the first timed model. It takes only computing time into account; all communication between the processing elements execute in zero time.

The next step in the refinement is the Scheduling Refinement (not shown in this graph). This refinement allows the designer to select suitable scheduling mechanisms to its processing elements. The scheduling capabilities range from an off-line static scheduling, which allows the most predictability, to a priority based dynamic scheduling.

The Communication design allows the user to select busses and protocols. Here the earlier defined abstract communication channels are mapped to physical busses and protocols. Detailed information about a utilized protocol is added. The resulting Communication model includes specific instructions for the particular bus implementation, like the access logic for a bus master or bus slave.

The synthesis step concludes the the design flow. Here the Register Transfer Level (RTL) code for the hardware will be generated with the prerequisite of RTL component allocation, their functional mapping and scheduling. As a result of the hardware synthesis a cycle accurate description of each hardware processing element is created. Similar activities take place for the software synthesis. Here specific code for the selected RTOS is inserted and target specific assembly code is compiled. The result is a cycle accurate model of each software-processing element, which can be simulated using an instruction set simulator and executed on the target processor. The combination of both synthesis parts is captured in the Implementation model, which gives a cycle accurate description of the whole system.

#### 1.2 Problem Definition

As it was described in the previous section the SoC design process is performed in several steps that formalize coping with the immense design space. Models of predefined standard components, such as basic communication elements, are needed for ease of design. Furthermore multiple models at different levels of abstraction are needed for each standard component, matching the stage within the design flow. An very abstract model can be used for fast high level exploration during early stages of the design, whereas a detailed model that yields most accurate results is needed for production validation.

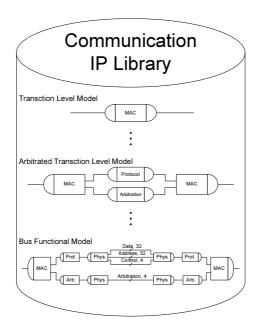

The scope of this work is to model a library communication component as symbolically depicted in Figure 1.3. In particular, AMBA was chosen since it reached, especially after introducing revision 2.0 of the standard in 1999, a wide acceptance for interconnections within a system-on-chip. With ARM's strong support for design, development and testing it pushed "right-first-time" development and the bus AMBA specification became one de facto standard for on-chip bus [2]. The goal this thesis work is to provide a bus functional model of an AMBA bus, that is synthesizable, and to model the bus as well at higher level of abstractions that allow a high simulation performance.

Figure 1.3: Scope of work: modeling of a communication IP (Symbolic Depiction)

Throughout the work appropriate levels of abstractions should be chosen for the abstract models. The implemented models should be validated against the standard with respect to functionality and timing accuracy. They should furthermore be compared to each other in terms of execution performance and simulation speed. Based on the experimental results a guideline should be made on how to choose the right model for a particular goal.

#### 1.3 Thesis Overview

In the remaining part of the thesis, first a general introduction to the AMBA bus gives the reader an overview of the specification. The overview is followed by the chapter on the actual design. The different models will be introduced. Their design will include a layered approach. Based on the design, accuracy expectations of each model will be described.

In the validation chapter (Chapter 4), the reader will find a functional and timing validation of the implemented models. Those validations will be made according to the specification [3].

The Chapter 5 shows measurements of the simulation speed and compares the accuracy of the individual bus models. It shows what trade offs the designer has to make for using a particular model. Finally Chapter 6 concludes the thesis and gives a summary.

#### 1.4 Related Work

System level modeling has become a more important issue over the recent years, as a means to improve the SoC design process. Languages for capturing these models have been developed, such as SpecC [10] or SystemC [14]. Furthermore capturing and designing communication systems using transaction level models has received research attention.

Sgroi et al. [21] address the SoC communication with a Network on Chip (NoC) approach. They propose partitioning of the communication into separate layers that follow the Open Systems Interconnection (OSI) structure. Software reuse is promoted with an increase of abstraction from the underlying communication framework.

Siegmund and Müller [22] describe an extension to SystemC, and propose modeling of a SoC at different levels of abstraction. They describe three different levels of abstraction: the physical description at RTL level, then a more abstract model that covers individual messages, and a most abstract level that deals with transactions.

In application of transaction level models [14], the topic of capturing communications within a SoC has received attention. In particular the widely used bus specification AMBA was the goal of modeling support.

Most relevant to this work is ARMs definition of the Cycle Level Interface (CLI) of the AMBA bus [1]. This specification defines how to implement the AMBA bus architecture in SystemC [20]. It has the goal of defining an interfacing standard between SystemC design models of IP components. It is intended to be used for system simulation and transaction based verification.

In [6] Caldari et al. describe the results of capturing the AMBA rev. 2.0 bus standard in SystemC. The bus system has been modeled at two levels of abstraction, first a bus functional model on RTL level and second a model on TLM level. Their Transaction Level Model (TLM) model reached a speedup of 100 over the RTL level model.

Another modeling approach of the AMBA bus architecture is shown in [23], where a transaction-based modeling abstraction level was described. While maintaining the bus cycle accuracy, this approach achieved a 55% speedup over the bus functional model.

CoWare [7] provides with ConvergenSC a commercial AMBA Transactional Bus Simulator. It allows for a fast cycle accurate architectural optimization and verification of an SoC design. With that it provides a solution for designing system-on-chip products that make use of AMBA bus specification and are described in SystemC.

## **Chapter 2**

### **Introduction to the AMBA Bus**

The Advanced Microprocessor Bus Architecture (AMBA) (see [3]) defined by ARM is a widely used open standard for an on-chip bus system. This standard aims to ease the component design, by allowing the combination of interchangeable components in the SoC design. It promotes the reuse of intellectual property components, so that at least a part of the SoC design can become a composition, rather than a complete rewrite every time.

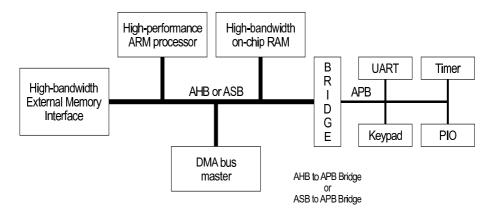

The AMBA standard defines different groups of busses, which are typically used in a hierarchical fashion. The Figure 2.1 shows a schematic overview of a typical microprocessor design. The design usually consists of a system bus; either the older version the Advanced System Bus (ASB), or the more performant Advanced High-performance Bus (AHB). All high performance components are connected to the system bus. Low speed components are connected to the peripheral bus, the Advanced Peripheral Bus (APB).

Figure 2.1: AMBA hierarchical bus architecture (Source [3]).

#### CHAPTER 2. INTRODUCTION TO THE AMBA BUS

The system busses ASB and AHB are designed for high performance connection of processors, dedicated hardware and on chip memory. They allow:

- Multiple bus masters

- Pipelined operation

- Burst transfers

The peripheral bus APB on the other hand is designed for low power peripherals with a low complexity bus interface. The APB can be connected via a bridge to both system busses AHB and ASB. The APB bridge acts as a master on the APB bus and all peripheral devices are slaves. The bridge appears as a single slave device on the system bus; it handles the APB control signals, performs retiming and buffering.

Between the two system busses the AHB delivers a higher performance than its older counterpart ASB. The AHB features:

- Retry and split transactions

- Single clock edge operation

- Non-tristate implementation

- Allows wider data bus configuration (e.g. 64 bits and 128 bits)

Retry and split transactions are introduced to reduce the bus utilization. Both can be used in case the slave does not have the requested data immediately available. In case of a retry transaction, the master retries the transaction after and own arbitrary delay. On the other hand in a split transaction the master waits for a signal from the slave that the split transaction can be completed.

One major factor for the high performance of the AMBA system busses is the pipelined access. For that, each bus access is executed in three separate stages, which can overlap between masters. The three phases for the pipelined bus access are:

**Arbitration Phase.** A master requests a bus access to the arbiter. The arbiter grants the access within an arbitrary number of bus cycles (at least one). Multiple masters may request the bus at the same time, however only a single master is granted at any given point in time.

**Address Phase.** The granted master applies the address and control signal to the bus. The address and control signals determine the activity for the next phase.

#### CHAPTER 2. INTRODUCTION TO THE AMBA BUS

**Data Phase.** Depending on the control signals from the previous phase (e.g. write direction) either the granted master or the selected slave write the data to the data bus.

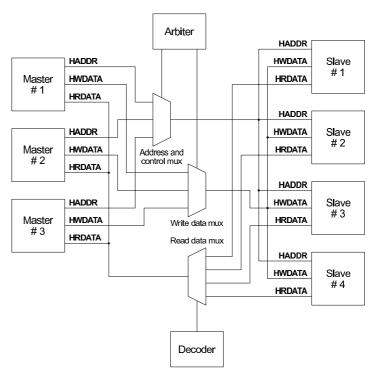

The AHB standard defines a non-tristate bus interface, which simplifies the design of the bus interfaces. It furthermore simplifies simulation of the bus system, since the costly three or four value logic - necessary for simulating a tristate interface - is not required. On the other hand, a non-tristate bus interface increases the number of connection for each bus interface; read and write bus have to be handled separately. This however is not a limiting factor, since the bus system is targeted for on-chip connections. It does, however, require an interconnection network, in which multiplexers select the bus access for each device. Figure 2.2 shows the AHB interconnection network.

Figure 2.2: Interconnection network for the AMBA AHB (Source [3]).

Three separate virtual busses, implemented by multiplexers, compose the interconnection network. The address / control bus (represented with HADDR) and the write data bus (represented with HWRITE) are written by each master. A slave writes to the own portion of the read data bus; a multiplexer selects the bus portion of the active device and distributes the selected signals. Since the AHB performs operation in a pipelined fashion, two separate multiplexers are necessary for the address / control bus and the write data bus; their access happens in separate stages of the pipeline.

## **Chapter 3**

# **Modeling**

As the introduction has motivated, high simulation speeds are necessary for an efficient design space exploration. High simulation speeds allow the designer to explore more solutions, thus increasing the chance of arriving at solution that is closer to the optimum. One possibility for a fast exploration is modeling at higher levels of abstraction (i.e. TLM) and gradually filling in details until a detailed synthesizable model is reached. In order to effectively support different levels of abstraction throughout the design process, a matching set of abstraction levels for library component is needed. Due to their frequent use this is especially true for bus components.

The following sections describe the design of the bus models for the AMBA AHB. First a generic layering approach will be introduced, which helps coping with the complexity of a bus simulation. The OSI layering scheme [15] was used as a reference for deriving those layers. The sections following that will describe each bus model in detail and show how the layered approach is applied.

### 3.1 Layering

A layered architecture was chosen for the communication system modeling in order to cope with the complexity of communication, in that it is similar to a general network stack implementation. [11] has introduced the applied layering structure as shown in Table 3.1. The layering structure was derived from the ISO OSI reference model [15].

Table 3.1 shows an overview of the layer separation, it also indicates where a particular layer is implemented and shows a representative code example for an invocation of each layer. The following list describes each layer in more detail. A full description can be found in [11, chapter 5].

| Layer           | Interface semantics                                                                               | Functionality                                                             | Impl.        | OSI |

|-----------------|---------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|--------------|-----|

| Application     | N/A                                                                                               | • Computation                                                             | Application  | 7   |

| Presentation    | PE-to-PE, typed, named messages •v1.send(struct myData)                                           | Data formatting                                                           | Application  | 6   |

| Session         | PE-to-PE, untyped, named messages  •v1.send(void*, unsigned len)                                  | • Synchronization • Multiplexing                                          | OS kernel    | 5   |

| Transport       | PE-to-PE streams of untyped messages • strml.send(void*, unsigned len)                            | <ul><li>Packeting</li><li>Flow control</li><li>Error correction</li></ul> | OS kernel    | 4   |

| Network         | PE-to-PE streams of packets •strm1.send(struct Packet)                                            | • Routing                                                                 | OS kernel    | 3   |

| Link            | Station-to-station logical links • link1.send(void*, unsigned len)                                | • Station typing • Synchronization                                        | Driver       | 2b  |

| Stream          | Station-to-station control and data streams  •ctrl1.receive()  •data1.write(void*,  unsigned len) | Multiplexing     Addressing                                               | Driver       | 2b  |

| Media<br>Access | Shared medium byte streams  •bus.write(int addr, void*, unsigned len)                             | • Data slicing • Arbitration                                              | HAL          | 2a  |

| Protocol        | <pre>Unregulated word/frame media transmission •bus.writeWord(bit[] addr, bit[] data)</pre>       | • Protocol timing                                                         | Hardware     | 2a  |

| Physical        | Pins, wires  •A.drive(0)  •D.sample()                                                             | • Driving, sampling                                                       | Interconnect | 1   |

Table 3.1: Communication layers (source [11]).

**Application Layer.** The application layer implements the computational functionality of the system. The layers basic content is defined by the designer during the specification and gradually implemented during the development process. During the design process the initial application specification is mapped onto individual Processing Elements (PEs). This application layer defines the system behavior and describes how the user data is processed in the system.

**Presentation Layer.** The presentation layer provides named channels, over which structures can be repeatedly transferred. The data structures are converted by the presentation layer into blocks of ordered bytes. Transmissions using the presentation layer are reliable. They can be synchronous or asynchronous.

Session Layer. The session layer is the interface between the software application and the Operating System (OS). It provides synchronous and asynchronous transport of untyped blocks of bytes. In case the lower layers do not provide synchronous access, synchronization will be implemented in this layer and an end-to-end synchronized access is realized. The channels provided by the session layer are used for identification of individual software entities. The session layer multiplexes multiple message blocks into an untyped message stream within the transmitting stack. Within the receiving stack, the session layer demultiplexes the incoming message stream into message blocks.

**Transport Layer.** The transport layer provides a reliable transmission of untyped streams between PEs in the system. The channels between the PEs act as pipes that carry the streams of the layers above. The transmission characteristics are generally asynchronous. The transport layer implements end-to-end flow control as a part of the operating system. The transport layer implement segmentation and reassembly, to split up the streams into smaller packets.

**Network Layer.** The network layer provides services for establishment of end-to-end paths, which carry the packet streams from the layers above. It completes the operating system kernel implementation for high-level end-to-end communication. The layer routes individual packets over point-to-point links, separating different end-to-end paths going through the same station. For a particular SoC design this routing could be static, and may even involve dedicated logical links.

**Link Layer.** The link layer provides services for the link establishment between two directly connected stations. It allows the exchange of uninterpreted packets of bytes. The link layer is the highest layer for a peripheral driver inside the operating system kernel. It defines the type of station (e.g. master / slave) and supports synchronization primitives (i.e. splits each logical link into a separate data and control stream).

**Stream Layer.** The stream layer implements services for transporting control and data messages between stations. It provides merging of multiple separate data/control streams over a single shared medium. It therefore provides addressing by which it separates the individual streams. The data messages are uninterpreted blocks of bytes. The format of the control messages is heavily implementation dependent (e.g. interrupt handling, polling). The transportation services are generally asynchronous and unreliable. However the reliability may depend on synchronization on higher levels (e.g. flow control).

Media Access Layer (1). The media access layer provides services for the transmission of a contiguous block of bytes over the selected media. The layer hides the specific implementation of the transmission medium, it is the lowest layer that provides a medium independent access. The media access layer provides data slicing, for that the incoming data transfer request, called the user transaction, is split into individual bus transactions. The size of the bus transactions depends on the medium.

**Protocol Layer (2).** The protocol layer provides transmission capabilities for individual bus transactions - words, shorts, bytes and defined lengths of blocks. The layer also performs arbitration for each bus transaction.

**Physical Layer (3).** The physical layer implements a bus cycle access to the physical wires. It performs sampling and driving of individual bus wires. Separate facilities are provided for accessing the data, address and control portion of the bus. The physical layer also provides all implementation necessary for the bus connection scheme, i.e. in case of the AHB the interconnection network consisting of multiplexers. Furthermore the physical implementation of arbitration is included.

For the work described in this thesis, parts of the library structure of the existing modeling environment, SoC Environment (SCE), have been reused. It was therefore not necessary to implement all of the layers above. Instead only the media specific layers - Media Access Layer, Protocol Layer and Physical Layer - have been implemented. Additionally it has been shown, that the link layer and the stream layer, although technically media dependent, are identical to a previous existing master slave bus model of the Motorola Master Bus, hence these layers have been reused.

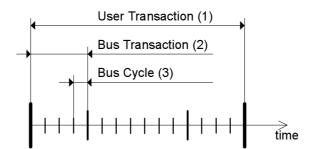

The following table lists the layers, that have been specifically implemented for the AMBA model. The table makes also a connection between the granularity of simulating the databus and the layering scheme, as an alternative explanation of the layering.

| Number | Layer              | Data Granularity |

|--------|--------------------|------------------|

| 1      | Media Access Layer | User Transaction |

| 2      | Protocol Layer     | Bus Transaction  |

| 3      | Physical Layer     | Bus Cycle        |

Table 3.2: Implemented layers and their granularity of data handling

The previous layer description was based on functional concerns. In an alternative view of the same layering scheme, the implemented layers can be described by using the granularity of data handling.

**User Transaction (1).** A user transaction is a request for transferring a contiguous block of data to or from a particular bus base address. The size of that request is arbitrary - independent of the bus limitations. The base address of the transfer is arbitrary as well. User transactions are used as an interface to the media access layer. They are then divided into one or more bus transactions.

**Bus Transaction (2).** A bus transaction is bus primitive. It supports transmission of individual elements such as byte, word or long. A particular bus (like the AHB) may also support transporting a collection of those individual elements, which are then transferred as a burst. The possible values for the bus transaction size and the requirements for the base address depend on the bus implementation (e.g. a bus transaction may not have a size of 3 bytes, or bursts have to start on a long aligned address). Bus transactions are used as an interface to the protocol layer. They are then transferred using the physical layer within one or more bus cycles.

**Bus Cycle (3).** The timed access to a synchronous bus is performed with a bus cycle granularity. During a bus cycle the values of wires/signals composing a bus may be changed. Typically this access is grouped by functionality, e.g. writing of address lines / control lines or reading of the data lines. The physical layer provides a bus cycle access to the bus.

The above defined levels of data granularity can also be analyzed with respect to time. Figure 3.1 shows how a user transaction is successively decomposed in time into the smaller elements: bus transaction and finally bus cycles. The coarse grain description of a user transaction, as accepted by the media access layer, is divided into one or more bus transactions. An individual bus transaction is transferred by the protocol layer in one or more bus cycle using the facilities of the physical layer.

Figure 3.1: Decomposition of a user transaction in time into bus transactions and bus cycles.

Following the concepts of system level modeling, each of the described layers was implemented in form of an individual channel. Using the channel concept allows a convenient handling of the abstraction levels. As an example the bus functional model requires all channels (all layers) for its operation, a more abstract model may reuse a subset of the defined channels and implement only one channel for the abstract simulation.

### 3.2 Graphical Notation

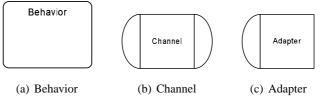

The graphical notation for the model description follows the definitions used in [10]. Figure 3.2 shows the main items that come to use.

Figure 3.2: Graphical notation for model description.

A behavior (Figure 3.2(a)) contains the computation part of the application. It has an own flow of execution. The system's functional behavior is captured in an hierarchy of behaviors.

A channel (Figure 3.2(b)) captures communication facilities. It does not have an own flow of execution. The services provided by a channel are described by an interface definition. Two behaviors may communicate through a channel, by mapping a port to an interface of the channel.

An adapter (Figure 3.2(c)), also called half channel, implements an interface to be mapped to another channel. The adapter does not have an own flow of execution.

#### 3.3 Transaction Level Model - MAC

The Transaction Level Model (TLM) is the most abstract model; it is expected to yield the fastest simulation speed. This model implements only the media access layer, therefore it is sometimes referred as the MAC model. User data, regardless of its size, is transferred in one chunk as one user transaction. The bus access is checked only once for the whole user transaction. The fact that the user transaction would be split into many bus transactions is ignored in order to reach higher simulation speeds. The TLM is not wire accurate. The communication is performed on a more abstract level than pins and wires. The model is not cycle accurate in all cases.

Figure 3.3 shows the connection schema for two masters and two slaves for the TLM model. The bus is simulated by a single channel implementing the media access layer; all masters and slaves directly connect to it. There is no distinction made between the masters connected to the bus, hence no priority based access between the masters is observed. Instead concurrent access to the bus is avoided by use of a semaphore, hence the order of concurrency resolution relies on the simulation environment.

Figure 3.3: Transaction Level Model (MAC model) connection scheme

In the model implementation done for this thesis, the user data is transferred using a single *memcpy* between master and slave. The timing is simulated by a single *waitfor* statement covering the whole user transaction. The calculation of the wait time takes into account the way the transaction would be split into bus transaction. A high simulation speed is expected due to the fixed low number of operations per user transaction.

Two variances of this model were defined for evaluation purposes. The TLM variance A (TLM (a)) performs as described, concurrent access is sequentialized by the use of a semaphore. The TLM variance B on the other hand does not prohibit concurrent access. As a result two masters may access the bus at the same simulated time. One of the two variances will be selected during the evaluation process.

#### 3.4 Arbitrated Transaction Level Model - Protocol

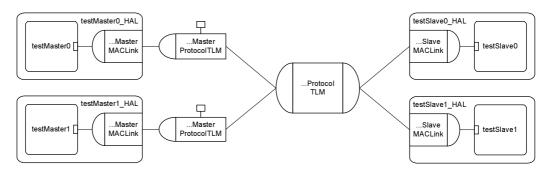

The Arbitrated Transaction Level Model (ATLM) simulates the bus access in the granularity of bus transactions, at the level of the protocol layer<sup>1</sup>. It is the first to perform arbitration, which is done as well at the level of bus transactions. To compose the ATLM, the medium access layer implementation is reused from the later described bus functional model. The medium access layer slices a user transaction into individual bus transactions, which are then transferred using the protocol layer implementation for this model.

<sup>&</sup>lt;sup>1</sup>Outside of this work the Arbitrated Transaction Level Model may also be referred to as the protocol model. It may be even understood as a Transaction Level Model since the TLM carries only a broad definition.

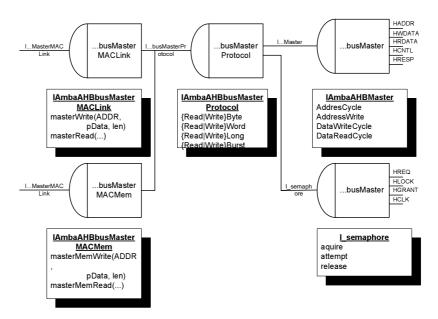

Figure 3.4 shows the symbolic bus scheme. A hardware abstraction layer is created around each application behavior. The channel for the media access layer in inlined into the hardware abstraction layer and the application behavior is connected to this channel. The bus is simulated by the channel implementing the protocol layer. The slaves are directly connected to this channel. The masters on the other hand are connected through individual half channels (MasterProtocolTLM), which are required for defining the master's identity. The identity is necessary for accurately simulating arbitration. The scheme 'identity through connectivity' was chosen for modeling of the master's identity, since it closely resembles the physical implementation, where the master's identity is defined by its connection to the arbiter.

Figure 3.4: Arbitrated Transaction Level Model (protocol model) connection scheme.

Since the ATLM implements the protocol layer as the lowest layer, it has to provide arbitration capabilities. With the previously described identity of each master, an accurate arbitration can be provided. The AHB definition does not require a specific arbitration scheme, so a priority based arbitration was implemented. In this model arbitration is performed on the granularity of a bus transaction. The arbitration scheme was implemented without an additional context switch (in addition to the executing masters), in order to ensure fast execution speed.

The ATLM with its arbitration per bus transaction is expected to be accurate already in case of locked transfers. In such transfers, a granted master may not be preempted during bus transaction, not even by a higher priority master. Hence all arbitration decision are done on a bus transaction boundary. However for unlocked transfers an inaccuracy is expected, here the bus owner ship may change even within a bus transaction (i.e. when a burst of a low priority master gets preempted by a high priority master).

As with the TLM, two variances have been created for the ATLM. The variances differ in the accuracy of the arbitration. The first variant of the ATLM, the ATLM (a), follows the concept of a delta cycle as it is used in hardware simulators. During a simulation two masters may attempt

an bus access at the same simulated time. However due to the serialized execution of the simulation code, one master's code will be executed earlier. In order to handle this situation the ATLM (a) does first collect all bus requests during one delta cycle and then makes the decision based on the collected requests. The ATLM (b), on the other hand, does not collect the bus requests for a delta cycle; it makes the decision immediately at the arrival of the first request. As a result, in case that two masters request the bus within the same delta cycle, the master with the earlier executed simulation code will gain bus access regardless of the priority.

A lower execution speed over the TLM is expected for both variances of the ATLM. Each individual bus transaction is modeled in terms of timing and arbitration individually. In terms of execution speed, the ATLM is expected to outperform the bus functional model, which covers the bus in all detail.

### 3.5 Bus Functional Model - Physical

The bus functional model is a synthesizable model bus model that covers all timing and functional properties of the bus definition. Communication is performed at the level of pins and wires. It is a wire accurate and cycle accurate model of the bus.

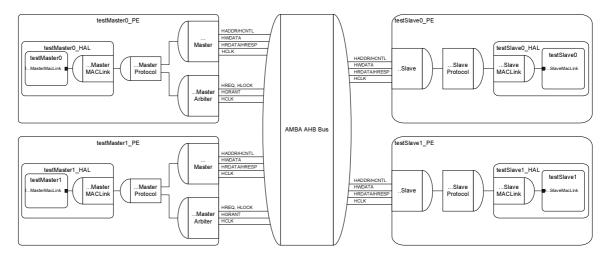

Figure 3.5: Bus functional model connection scheme.

Figure 3.5 shows how the application behaviors are wrapped for the bus functional access. As described for the ATLM, each application behavior is first wrapped in the hardware abstraction layer that inlines a half channel implementing the Media Access Control (MAC) layer. For the bus functional model each bus element is further wrapped into a processing element. The processing

element inlines a channel instance that implements the protocol layer, where the MAC channel is connected to. Additionally a channel implementing the physical access is inlined. As a result each processing element is connected via wires to the actual bus.

Figure 3.6: Content of the bus functional channel.

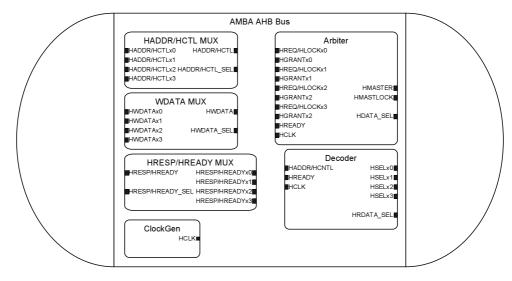

For ease of understanding, the bus in Figure 3.5 is graphed as a channel. However the bus consists of many individual elements as the Figure 3.6 shows. Since the AHB definition defines the bus access without tristate outputs, a set of multiplexers is required to select address, data and control signals from the active bus components. Additionally the bus functional implementation contains a clock generator, an arbiter and an address decoder. Please refer back to Figure 2.2 for an overview of the AHB interconnection scheme.

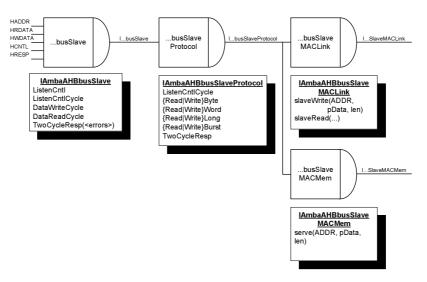

As it can be seen by the inlined channels, the bus functional model uses all described layers. Actual wires are used for the connection of the bus elements. The bus wires are driven and sampled according to the AMBA specification with the rising edge of the bus clock. The physical layer provides the access to the bus on a bus cycle basis. The services of the physical layer are used by the protocol layer, which implements arbitration and data transfer. The arbitration is done for each bus transaction, and for unlocked burst the bus grant state is verified additionally on each bus cycle. As in the ATLM the protocol model is invoked by the MAC layer, which slices the user transaction into bus transactions. Figure 3.7 and Figure 3.8 show an overview of the implemented channels for the master and slave side respectively.

Figure 3.7: Channels for master bus functional model.

Figure 3.8: Channels for slave bus functional model.

#### 3.6 Modes of Access

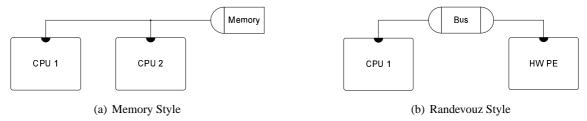

The utilized design environment SCE defines two distinct ways of accessing bus slaves, namely the memory style access and the rendezvous style access (also referred to as link style access). Both styles are depicted in Figure 3.9.

Figure 3.9: Modes of access

In a memory style access (Figure 3.9(a)), the slaves accessible memory is exposed to the bus over an address range. A master may access the provided address range at any point in time. This access style is applicable for memory and for memory mapped IO. This style of access allows burst accesses for improved performance. The abstract notation in Figure 3.9(a) indicates the memory as a half channel, which was made to show that the memory has no own flow of execution.

The rendezvous type access (Figure 3.9(b)), simulates a message passing interface. The slave only exposes a single address to the bus for each rendezvous type access. The content of a user transaction is written one-by-one to the same base address. With that a mailbox is simulated on the slave side. This is especially useful if the address space is limited, since the message length does does not influence the required address space. In a rendezvous style access a slave waits for an access on a particular address and further reacts to the request. Application level synchronization is needed for this model, since the access patterns have to be known on the slave side. The depiction of the rendezvous style access (Figure 3.9(b)), presents the slave (HW PE) as an own PE, thus it is shown to have an own flow of execution.

Since the rendezvous type access simulates a message passing interface, all words within a message are written to the same address. Due to this addressing pattern bursts can not be used, since the AHB specification requires to increase the address for each beat within a burst. Hence a user transaction in the rendezvous style access is transferred only with individual non sequential transfers.

In order to support both styles of access, two channel implementations of the MAC layer are provided. One channel per access type, the simulation environment generates code, that instantiates both channels and uses the appropriate channel for a particular transfer.

## **Chapter 4**

### **Validation**

The previous chapters have presented the design and implementation of the AMBA AHB bus. In this chapter covers the validation results. Three aspects will be described in more detail. First, the functional validation is described in Section 4.1. Those tests aim to assert the correct functionality ignoring timing constraints. Following that, Section 4.2 describes the validation of the timing accuracy of the bus functional model. Finally, Section 4.3 will deal with the timing correctness of the abstract models, the ATLM and TLM. Throughout this chapter no differentiation is made between the two variations of each of the abstract models. Thus, using the generic model name refers to both variations.

### 4.1 Functional Validation

In an early part of the validation, the functional correctness of each AMBA AHB bus model is validated. Following a bottom up approach, a first set of tests will focus on individual bus transactions. Later more complex access patterns and corner cases are verified with the randomized tests utilizing the memory style MAC layer and the rendezvous style MAC layer.

### 4.1.1 Validation of Individual Bus Transfers – Fundamental Tests

The goal of the fundamental tests validating individual bus transfers is to ensure correct functionality of the bus primitives. The test provides the foundation for the construction of more complex tests. The following sequence of test was performed using the memory style MAC layer of each implemented model:

- Single Master Single Slave validates that each basic bus transaction yields the correct results. It validated read and write functionality for Byte, Word (16Bit), Long, fixed length burst (for 4, 8, and 16 beats).

- Single Master Dual Slave validates the connectivity and selection of multiple slaves addressed by a single master.

- Dual Master Single Slave introduces testing of the arbitration and validates that the bus is accessed exclusively by a single master as a result of arbitration.

- Dual Master Dual Slave validates the functional independent access to the bus for two master/slave pairs.

Figure 4.1 shows the logical connection scheme for each of the test groups. A range of predefined data was transferred to/from a set of predefined addresses for each individual test within a test group. A test was concluded successful if all data arrived correctly, in the predefined order, at the predefined addresses. Additionally *assert* statements have been manually introduced at critical places into the channel implementations, to detect invalid states within a channel. The results of the validation are shown in Table 4.1. All tests for all test groups have successfully passed for each implemented model. Hence a correct functional behavior is expected from each model.

(a) Single master single slave (b) Single master dual slave (c) Dual master dual slave (d) Dual master dual slave parallel interleaved

Figure 4.1: Logical connection for individual bus transfer validation.

|                                                    | Bus        | Arbitrated  | Transaction |

|----------------------------------------------------|------------|-------------|-------------|

|                                                    | Functional | Transaction | Level       |

| Logical Connection under Test                      | Model      | Level Model | Model       |

| Single master single slave, Fig 4.1(a)             | passed     | passed      | passed      |

| Single master multi slave, Fig 4.1(b)              | passed     | passed      | passed      |

| Multi master multi slave (parallel), Fig 4.1(c)    | passed     | passed      | passed      |

| Multi master multi slave (interleaved), Fig 4.1(d) | passed     | passed      | passed      |

Table 4.1: Results of individual bus transfer validation

#### **4.1.2** Validation of the Memory Interface

After having successfully validated individual bus transactions, now complex access patterns consisting of multiple bus transactions will be validated. This validation uses random access patterns, which statistically cover all access scenarios in accessing the components if executed long enough. The focus for this validation is the random interaction between two masters that access the same bus.

Two masters and two slaves are implemented for this test. The access is performed using the random access type. The memory exposed by the slaves present separate address regions for writing and reading. The following parameters are randomized for each transaction: read/write, the size of the transaction, the offset within the memory and the delay between transactions. The random selection algorithm ensures that each byte of the slave's memory is accessed exactly once during the test. Throughout the test the base address and the length of the user transaction, to be transfered, will vary. The way the MAC layer breaks down a user transaction into one or more bus transactions depends on exactly these two parameters. As a result the sequence of bus transactions per user transaction will vary throughout the test. This diversity is a good test for the slicing functionality of the MAC layer. The delay between the operations results in a random access pattern between the masters. This will test the arbitration implementation and validate the exclusive access to the bus in scenarios like concurrent bus request, back to back transmission, and handover between a high priority master and a low priority master. The correctness of each user transaction is validated directly after executing the user transaction; the master and slave memory area is compared for equality. Furthermore, after completing all user transactions, the complete memory area of master and slave are compared for equality as well.

In comparison to the earlier fundamental tests, not all of its configurations had to be retested. The utilized connection schemes are displayed in Figure 4.2. For a successful validation of a single connection scheme and bus model, two masters have to transfer 128KBytes each, using a random set of user transactions of up to 100 bytes each. The test has to fulfill the criteria in the previous paragraph and sustain the results for 1000 test repetitions. With an average user transaction size of 50 bytes, each bus model and connection scheme was validated with more than 2.5 million user transactions. Table 4.2 indicates the results of this test scenario, and shows that the test execution was successful for all configurations and all bus models.

- (a) Dual master single slave

- (b) Dual master dual slave parallel

- (c) Dual master dual slave interleaved

Figure 4.2: User level logical connection for memory and rendezvous type access validation.

|                                                     | Bus        | Arbitrated  | Transaction |

|-----------------------------------------------------|------------|-------------|-------------|

|                                                     | Functional | Transaction | Level       |

| <b>Logical Connection under Test</b>                | Model      | Level Model | Model       |

| Multi master single slave, Fig. 4.2(a)              | passed     | passed      | passed      |

| Multi master multi slave (parallel), Fig. 4.2(b)    | passed     | passed      | passed      |

| Multi master multi slave (interleaved), Fig. 4.2(c) | passed     | passed      | passed      |

Table 4.2: Results of validation for memory access

#### 4.1.3 Validation of the Rendezvous Interface

In addition to the randomized test using the memory access style MAC layer, the rendezvous style MAC layer has to be verified as well. The two implementations differ in the way they slice the data. Here again random accesses have been utilized, varying the following parameters: read/write, size, offset, delay between accesses. In difference to the previous validation, only the independent access of two master slave pairs was tested (Fig. 4.2(b)). The other two connection schemes (Multi Master Single Slave and Multi Master Multi Slave (interleaved)) were not tested, since they are not applicable in the used simulation environment.

For the rendezvous style access, the simulation environment makes the assumption, that each access is predictable. As a result of the assumption, the slave code has to be implemented so that a particular user transaction is expected. Now, if two masters simultaneously request access to different portions of the slave's memory, the slave has to predict which user transaction is executed first. Since this depends on the arbitration, it is declared undecidable for a slave. In such situations, the memory style access should be used, hence the configurations are not applicable for this test.

Limiting the validated configurations does not limit the generality. The two access styles for the MAC layer differ in how a user transaction is sliced into bus transactions. This feature can be validated in any connection scheme. On the other hand the connection schemes differ in the way they create contention. The contention however is handled by the lower layers, which already have been successfully tested during earlier tests.

Table 4.3 summarizes the performed functional validations with the same set of connection schemes as before (Figure 4.2). The same execution criteria as for the memory interface validation were used here. Thus more than 2.5 million user transactions had to be transferred correctly for a successful validation of one bus model and connection scheme. The table shows successful test execution for the tested configuration for the three abstraction levels: bus functional, arbitrated transaction level modeling and transaction level modeling.

|                                                     | Bus        | Arbitrated  | Transaction |

|-----------------------------------------------------|------------|-------------|-------------|

|                                                     | Functional | Transaction | Level       |

| <b>Logical Connection under Test</b>                | Model      | Level Model | Model       |

| Multi master single slave, Fig. 4.2(a)              | N/A        | N/A         | N/A         |

| Multi master multi slave (parallel), Fig. 4.2(b)    | passed     | passed      | passed      |

| Multi master multi slave (interleaved), Fig. 4.2(c) | N/A        | N/A         | N/A         |

Table 4.3: Results of functional verification of rendezvous access

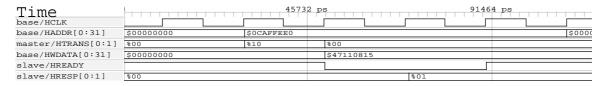

## **4.2** Timing Validation of the Bus Functional Model

Considering the results of the previous section, a correct functional behavior of all implemented models can be expected. Additionally important is a timing validation, which deals with the correct behavior of each signal in the temporal sense. This is particularly important for the synthesizable bus functional model, as a prerequisite for interoperability with other intellectual property components.

A validation of the timing behavior requires an independent reference. Since a physical implementation of the modeled bus structure was not available in the lab at the point of writing, the timing behavior of the model was compared against the specifications. The following sections will show the comparison of the implemented bus functional model against transfer scenarios selected from two sources: the AMBA specification [3] and the AMBA AHB Cycle Level Interface [1], which is an interpretation of the AMBA specification.

The selected scenarios have been be recreated with the implemented bus functional model, which in this setup simulates a bus with 50MHz bus clock. Additional probes have been inserted into the test bench for tracing of all important bus wires. The traces are displayed as waveforms, which have been generated using *gtkwave* (see [5]).

#### 4.2.1 Basic Pipelined Bus Access

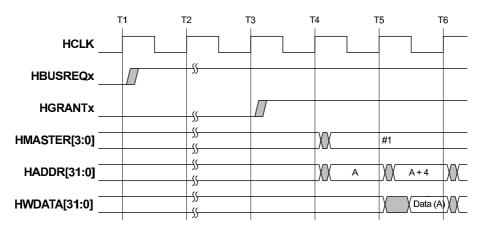

As described in Chapter 2, the AHB allows a pipelined access to the bus. The basic stages of the pipelined bus access are validated in the first pair of waveforms.

Figure 4.3 shows the reference waveform and Figure 4.4 displays the results of the actual implementation. As a general note, the specification [3] requires signals to be valid at the rising edge of HCLK, at this point the signals are sampled from participating bus elements (which are all implemented as sequential logic, see [4, question #4120]). The implemented model does not cover subcycle events, therefore each signal is applied immediately after the rising clock edge. Hence there will be an acceptable subcycle difference between the reference and the implemented model.

Figure 4.3: Reference sequence from [3] showing pipelined behavior

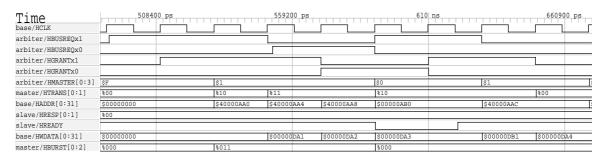

| Time                 | 86593300 ps     | 866279     | 900 ps     | 866624     | 100 ps |

|----------------------|-----------------|------------|------------|------------|--------|

| arbiter/HBUSREQx1    |                 |            |            |            |        |

| arbiter/HGRANTx1     |                 |            |            |            |        |

| arbiter/HMASTER[0:3] | \$1  \$0        |            | \$1        |            | \$0    |

| base/HADDR[0:31]     | \$+  \$0CB040E0 |            | \$4CB040E0 |            | \$0CE  |

| base/HWDATA[0:31]    | \$471108E0      | \$47110817 |            | \$471108E0 |        |

Figure 4.4: Waveform of implemented bus model, showing pipelined behavior

The following three points within the displayed transfer are of interest for deciding the timing correctness of the implementation:

1. In bus cycle T1, the master requests bus access. Within an arbitrary number of bus cycles (at least one) the arbiter grants access to the bus. In the particular reference waveform, the arbiter grants the access in T3. In the waveform of the implemented model, the bus is requested in

the first clock cycle and granted in the second. Again, granting the bus within a single cycle is valid, an example of a one-cycle-grant can be found in the reference waveform in Figure 4.7.

- 2. In the bus cycle after granting the bus<sup>1</sup>, the granted master applies the address and control signals to the bus. This happens in the reference in T4 and in the actual implementation in the third bus cycle, which is in both cases the cycle after the bus grant.

- 3. The data is written in the bus cycle after applying address and control information. The reference waveform shows this in T5, the actual implementation shows it in the fourth cycle. In both cases it happens in the cycle directly following the address and control signals. As it will be seen in later waveforms, the pipelined access allows concurrently applying the data for one cycle and the address and control lines for the next cycle.

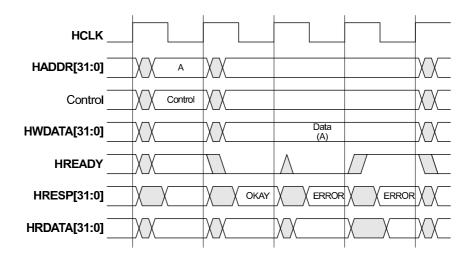

#### 4.2.2 Error Response

The previous subsection has shown that the basic pipeline stages are observed by the implemented model. This behavior was shown under the assumption that the selected slave always signals to proceed with the current transfer. In this subsection this restriction will be removed.

The AHB standard defines that a slave has to reply back to the master for each bus operation. This reply indicates the success of the bus operation and is done on every bus cycle. Multiple slaves may be selected in different phases of the transfer due to the pipelined access nature of the AHB. However, only the selected slave that is in the data phase asserts the reply information. The reply information is provided by the following two signals:

**HREADY** is used by the slave to extend the the data portion of an AHB transfer. The slave inserts a wait state in the bus access by asserting LOW to HREADY. A transfer is finished regardless of the success once HREADY is HIGH.

**HRESP** is asserted by the slave and indicates the status of the current transfer. Possible values are OKAY, ERROR, SPLIT and RETRY. OKAY indicates a successful completion of the bus operation. The latter three result codes indicate additional handling for this operation and they require a two-cycle response. With a two-cycle response the pipeline of the bus access is flushed.

$<sup>^{1}</sup>$ A simplifying assumption is made for this subsection: the currently selected slave signals to proceed with the transfer, which is done by asserting HRESP == OKAY, and HREADY == HIGH.

Figure 4.5 shows how a slave indicates a failed transfer. By setting HREADY to low, the slave inserts one additional wait state to make the decision about the transfer. The following timing points are of interest in order to validate implemented model as shown in Figure 4.6:

- In the bus cycle following the address phase, the slave asserts HREADY to LOW and inserts

a wait state. This happens in the second cycle in the reference and in the third cycle of the

implementation waveform.

- 2. The slave has made the decision of failing the bus transfer in the third cycle of the reference waveform. At that point it starts the first cycle of the two-cycle error response. The slave applies the value of ERROR to HRESP. This happens in both waveforms in the cycle after the first wait state.

- 3. In the second cycle of the two-cycle error response the slave still applies ERROR to HRESP. In order to finish the bus transaction HREADY is set to HIGH. This behavior can be observed in both waveforms in the second cycle after the first wait state.

Figure 4.5: Reference sequence from [3] showing an error response

Figure 4.6: Waveform of implemented bus model, showing error response

#### 4.2.3 Unlocked Burst Handover