## Hint-Assisted Scheduling on Modern GPUs

A Dissertation Presented

by

Xun Gong

to

## The Department of Electrical and Computer Engineering

in partial fulfillment of the requirements for the degree of

**Doctor of Philosophy**

in

**Computer Engineering**

Northeastern University Boston, Massachusetts

April 2020

ProQuest Number: 27955816

All rights reserved

INFORMATION TO ALL USERS The quality of this reproduction is dependent on the quality of the copy submitted.

In the unlikely event that the author did not send a complete manuscript and there are missing pages, these will be noted. Also, if material had to be removed, a note will indicate the deletion.

ProQuest 27955816

Published by ProQuest LLC (2020). Copyright of the Dissertation is held by the Author.

All Rights Reserved. This work is protected against unauthorized copying under Title 17, United States Code Microform Edition © ProQuest LLC.

> ProQuest LLC 789 East Eisenhower Parkway P.O. Box 1346 Ann Arbor, MI 48106 - 1346

# Contents

| Lis | st of F | ligures                                           | iv   |

|-----|---------|---------------------------------------------------|------|

| Lis | st of T | <b>Tables</b>                                     | vi   |

| Ac  | know    | ledgments                                         | vii  |

| Ab  | strac   | t                                                 | viii |

| 1   | Intro   | oduction                                          | 1    |

|     | 1.1     | Growth of the GPU Market                          | 1    |

|     | 1.2     | GPU Computing Model                               | 4    |

|     | 1.3     | Resource Underutilization                         | 4    |

|     | 1.4     | Motivation of this thesis                         | 5    |

|     | 1.5     | Challenges                                        | 7    |

|     |         | 1.5.1 Lack of GPU Simulation Framework            | 7    |

|     |         | 1.5.2 Lack of Control Logic                       | 8    |

|     |         | 1.5.3 Intensive Memory Contention in GPUs         | 9    |

|     | 1.6     | Contributions of This Thesis                      | 9    |

|     | 1.7     | Organization of Thesis                            | 10   |

| 2   | Back    | sground                                           | 11   |

|     | 2.1     | History of GPU computing                          | 11   |

|     | 2.2     | GPU Evolution                                     | 12   |

|     | 2.3     | SIMT Programming Model                            | 14   |

|     | 2.4     | GPU Architecture                                  | 16   |

|     |         | 2.4.1 Steaming Multiprocessor Architecuture       | 16   |

|     |         | 2.4.2 GPU Memory Hierarchy                        | 16   |

|     | 2.5     | Warp Scheduling                                   | 19   |

|     |         | 2.5.1 Scheduling Algorithms                       | 19   |

| 3   | Rela    | ted work                                          | 20   |

|     | 3.1     | Using Hinting in Microprocessors                  | 20   |

|     | 3.2     | Warp Scheduling                                   | 21   |

|     | 3.3     | Exploiting Thread Level Parallelism (TLP) on GPUs | 22   |

|   | 3.4  | Improv         | ving Instruction Level Parallelism on GPUs | 24       |

|---|------|----------------|--------------------------------------------|----------|

|   | 3.5  | Improv         | /ing GPU memory hierarchy utilization      | 25       |

|   | 3.6  | GPU S          | imulation Frameworks                       | 26       |

| 4 | Sim  | ulation        | Framework 2                                | 28       |

|   | 4.1  | Simula         | tion Methodology                           | 28       |

|   | 4.2  |                | ••                                         | 29       |

|   |      | 4.2.1          | ••                                         | 29       |

|   |      | 4.2.2          |                                            | 31       |

|   | 4.3  |                |                                            | 31       |

|   |      | 4.3.1          |                                            | 31       |

|   |      | 4.3.2          | 1                                          | 34       |

|   |      | 4.3.3          |                                            | 36       |

|   |      | 4.3.4          | 1                                          | 37       |

|   | 4.4  |                |                                            | 39       |

|   | т.т  | 4.4.1          |                                            | 39       |

|   |      | 4.4.2          |                                            | ,,<br>12 |

|   |      | 4.4.2          | 8                                          | +2<br>14 |

|   |      | 4.4.3<br>4.4.4 |                                            | +4<br>16 |

|   | 15   |                | 1                                          | +0<br>47 |

|   | 4.5  | Summa          | ary                                        | +/       |

| 5 | Hint | t-Assiste      | ed Warp Scheduling 4                       | 18       |

|   | 5.1  | Selecti        | ve Out-of-order Execution                  | 18       |

|   | 5.2  | Hint A         | ssisted Execution                          | 50       |

|   | 5.3  | Microa         | rrchitecture of HAWS                       | 52       |

|   |      | 5.3.1          |                                            | 52       |

|   |      | 5.3.2          | Compiler Work                              | 54       |

|   |      | 5.3.3          | *                                          | 54       |

|   |      | 5.3.4          |                                            | 57       |

|   |      | 5.3.5          |                                            | 58       |

|   |      | 5.3.6          | 6                                          | 50       |

|   | 5.4  |                |                                            | 51       |

|   | 0.1  | 5.4.1          |                                            | 51       |

|   |      | 5.4.2          | <i>e</i> ;                                 | 52       |

|   |      | 5.4.3          |                                            | 52<br>53 |

|   |      | 5.4.4          |                                            | 55<br>55 |

|   |      | 5.4.5          |                                            | 55<br>57 |

|   | 5.5  |                |                                            | 57<br>57 |

|   | 5.5  | Summ           |                                            | ,,       |

| 6 |      |                |                                            | 59       |

|   | 6.1  |                |                                            | 59       |

|   | 6.2  |                |                                            | 70       |

|   | 6.3  |                | , .                                        | 74       |

|   |      | 6.3.1          |                                            | 75       |

|   |      | 6.3.2          | Locality Aware Scheduling                  | 76       |

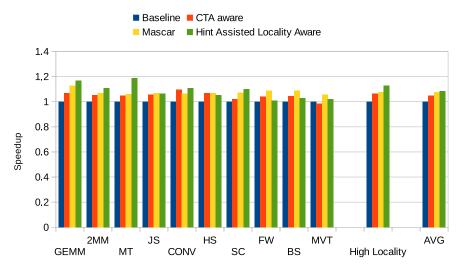

| 6. | 4 Evalua  | ation                                          |

|----|-----------|------------------------------------------------|

|    | 6.4.1     | Methodology                                    |

|    | 6.4.2     | Performance                                    |

|    | 6.4.3     | Reduction in Duplicated Cache Line Allocations |

|    | 6.4.4     | Number of Memory Requests per MSHR Entry       |

|    | 6.4.5     | Summary                                        |

|    | onclusion |                                                |

| 7. | 1 Conclu  | usion                                          |

|    |           |                                                |

# **List of Figures**

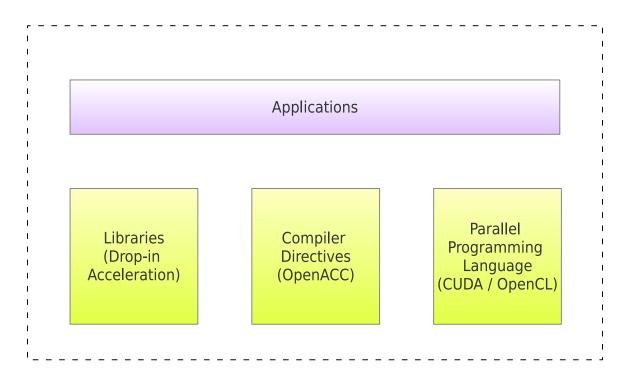

| 1.1  | Different ways to accelerate demanding applications.                                  | 3  |

|------|---------------------------------------------------------------------------------------|----|

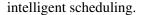

| 1.2  | Breakdown of scheduling cycles.                                                       | 6  |

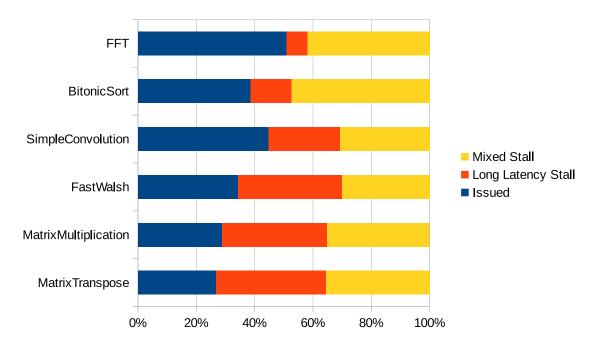

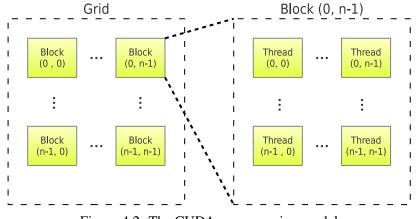

| 2.1  | The CUDA Programming Model.                                                           | 14 |

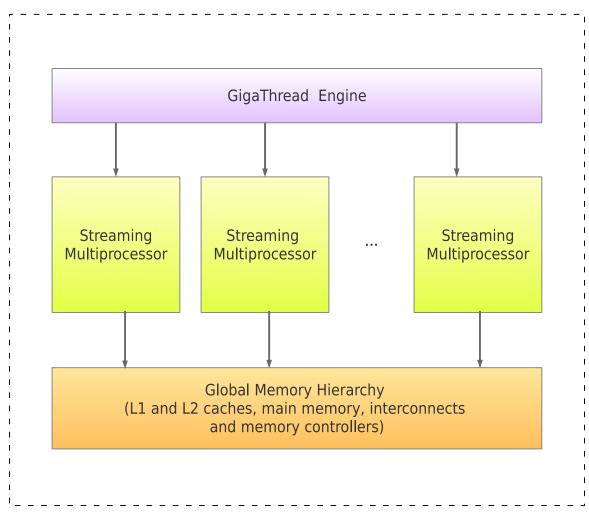

| 2.2  | A typical GPU architecture.                                                           | 15 |

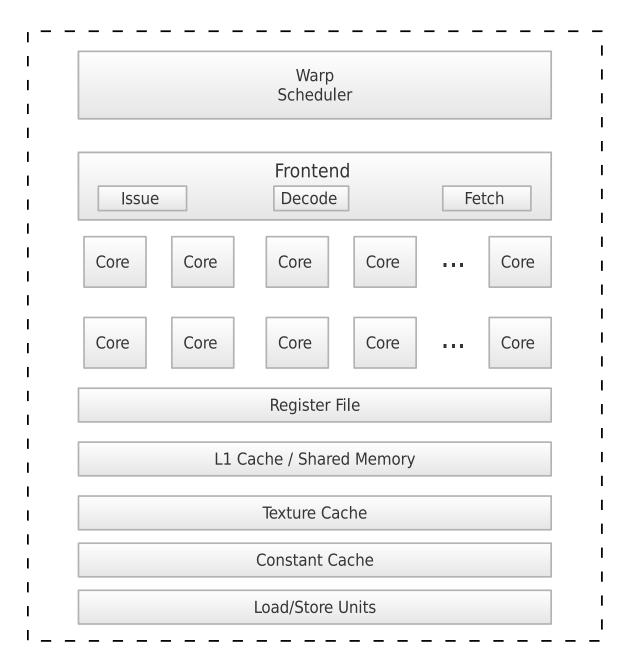

| 2.3  | A typical SM architecture.                                                            | 17 |

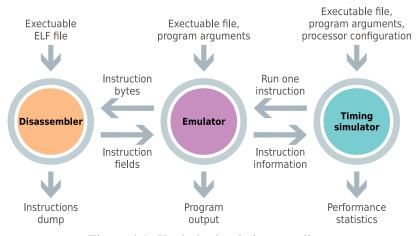

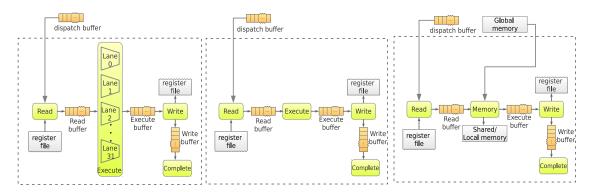

| 4.1  | Kepler's simulation paradigm.                                                         | 29 |

| 4.2  | The CUDA programming model.                                                           | 30 |

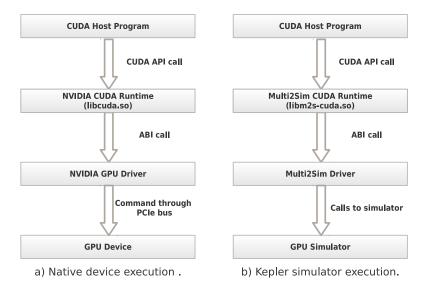

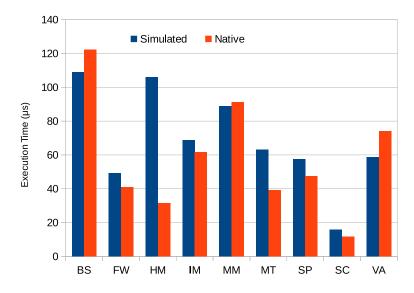

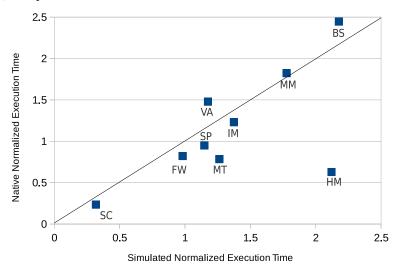

| 4.3  | Comparison of native and simulated Kepler execution environments.                     | 30 |

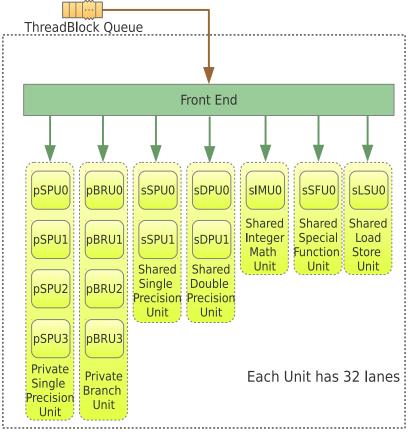

| 4.4  | Streaming Multiprocessor architecture.                                                | 32 |

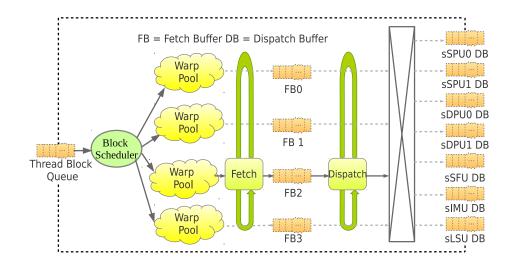

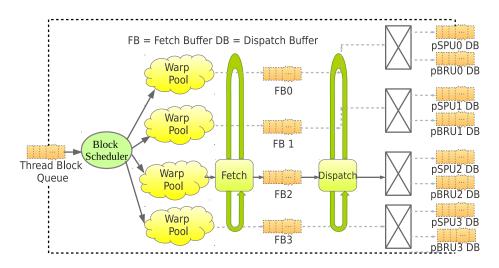

| 4.5  | A block diagram of the front-end pipeline.                                            | 33 |

| 4.6  | Sample SASS code                                                                      | 34 |

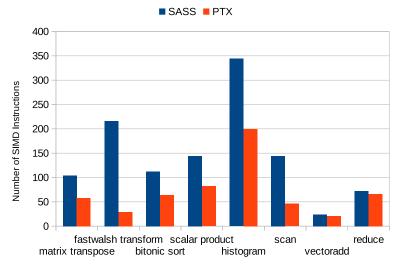

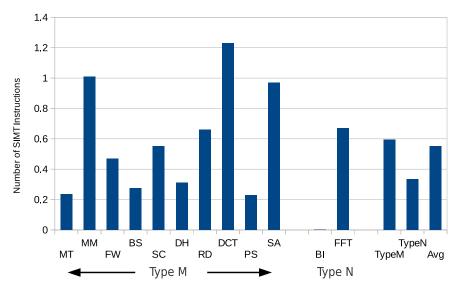

| 4.7  | The number of SIMD instructions in SASS and PTX.                                      | 35 |

| 4.8  | Pipeline of different units.                                                          | 37 |

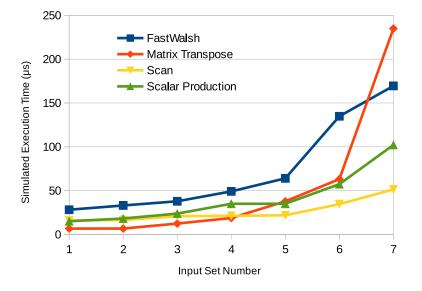

| 4.9  | Validation for the architectural simulation, comparing trends between simulated and   |    |

|      | native execution times.                                                               | 40 |

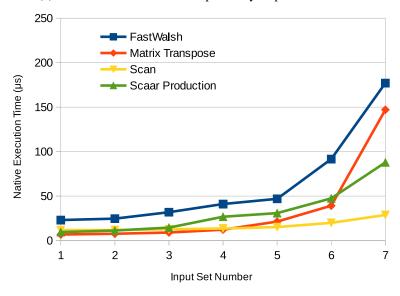

| 4.10 | Validation for the architectural simulation, comparing simulated and native execution |    |

|      | times                                                                                 | 42 |

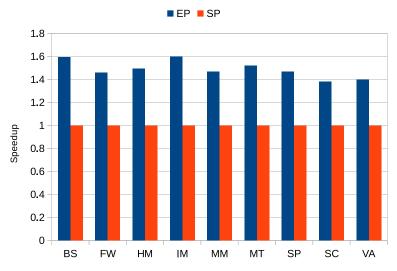

|      | Performance comparison between EP and SP                                              | 43 |

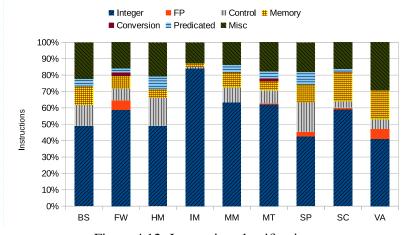

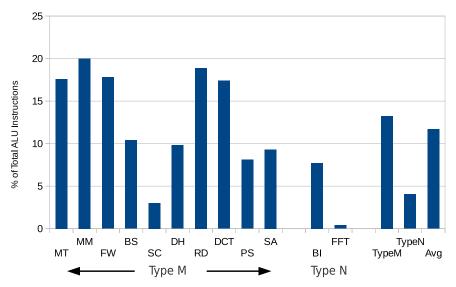

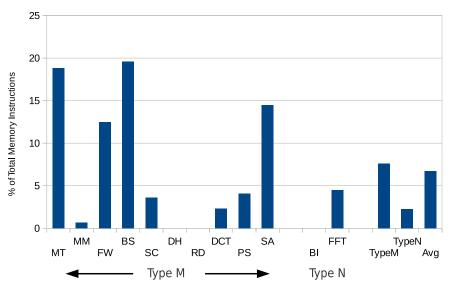

|      | Instruction classification.                                                           | 44 |

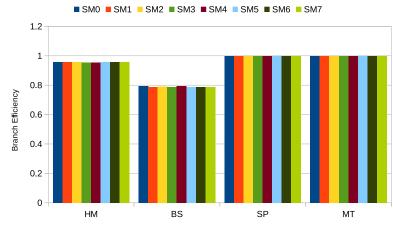

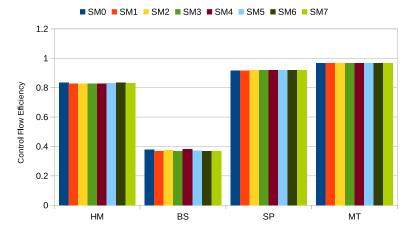

|      | Branch efficiency and control flow efficiency.                                        | 45 |

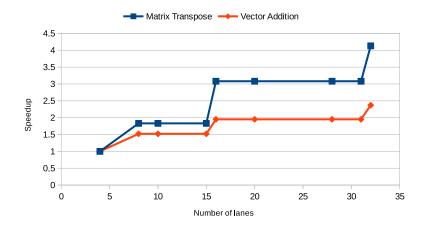

| 4.14 | Scaling the number of lanes.                                                          | 46 |

| 5.1  | Assembly instructions from a GPU kernel.                                              | 49 |

| 5.2  | Instruction sequences produced for different benchmarks                               | 50 |

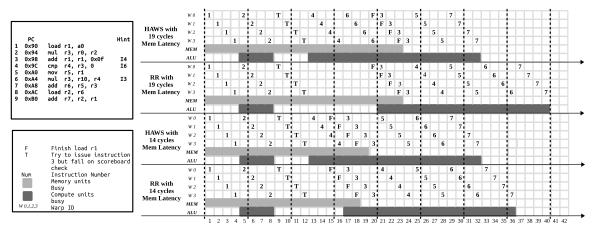

| 5.3  | Execution timeline for round-robin scheduler and HAWS. The Top 2 are running          |    |

|      | with a 19 cycles memory latency. The bottom 2 are running with a 14 cycles memory     |    |

|      | latency                                                                               | 51 |

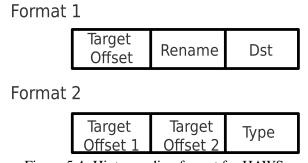

| 5.4  | Hint encoding format for HAWS                                                         | 52 |

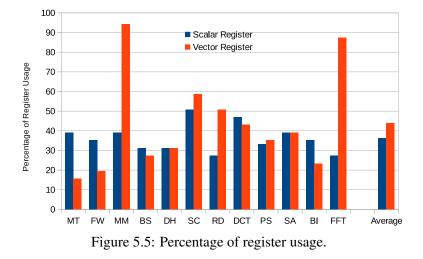

| 5.5  | Percentage of register usage.                                                         | 53 |

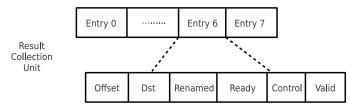

| 5.6  | Organization of Result Collection Unit.                                               | 56 |

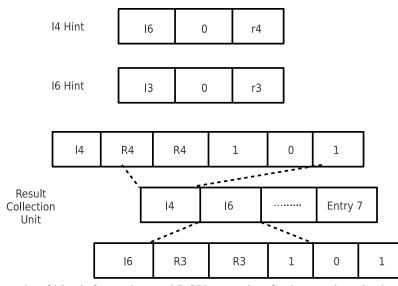

| 5.7  | Example of hint information and RCU operation for instructions in the first experi-         |     |

|------|---------------------------------------------------------------------------------------------|-----|

|      | ment of figure 5.1. For clarity, all offset fields are shown as the instruction it points   |     |

|      | to                                                                                          | 56  |

| 5.8  | Fetch logic.                                                                                | 58  |

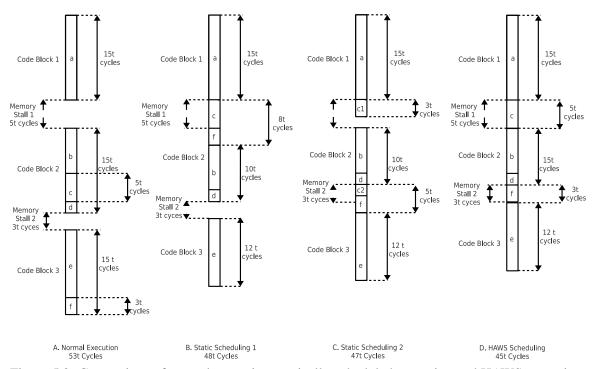

| 5.9  | Comparison of normal execution, statically-scheduled execution and HAWS execution.          | 59  |

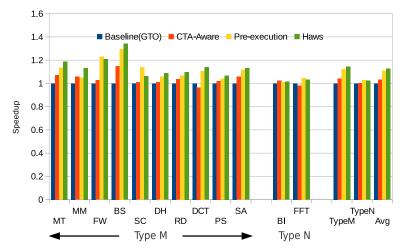

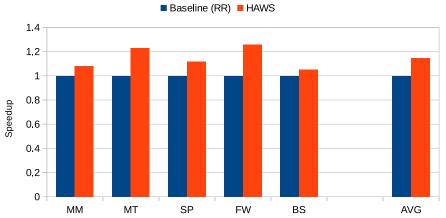

| 5.10 | ) Speedup of HAWS, relative to the baseline model                                           | 63  |

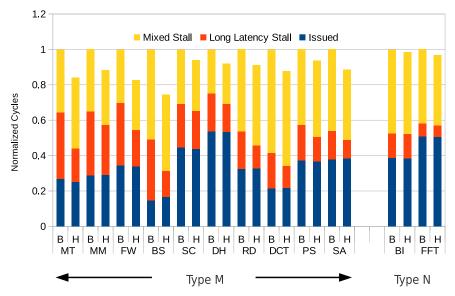

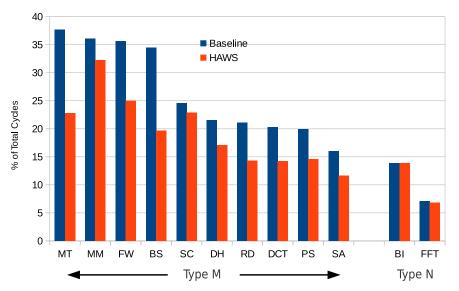

| 5.1  | Breakdown of Scheduling Cycles (B:Baseline, H:HAWS).                                        | 64  |

| 5.12 | 2 Percentage of long latency stall, comparing HAWS with baseline model                      | 64  |

| 5.13 | <sup>3</sup> Average number of SIMT instructions executed per warp for per HAWS scheduling. | 65  |

| 5.14 | Percentage of total ALU instructions executed by HAWS                                       | 66  |

| 5.15 | 5 Percentage of total Memory instructions executed by HAWS                                  | 66  |

| 5.10 | 5 Speedup of HAWS on simulated Kepler GPU                                                   | 67  |

| (1   | Description of MOUD allocated for deallocate and the line is a single first the             |     |

| 6.1  | Percentage of MSHRs allocated for duplicate cache lines in a given time. The                | 70  |

| ()   | window size is 2000 cycles in the diagram.                                                  | 70  |

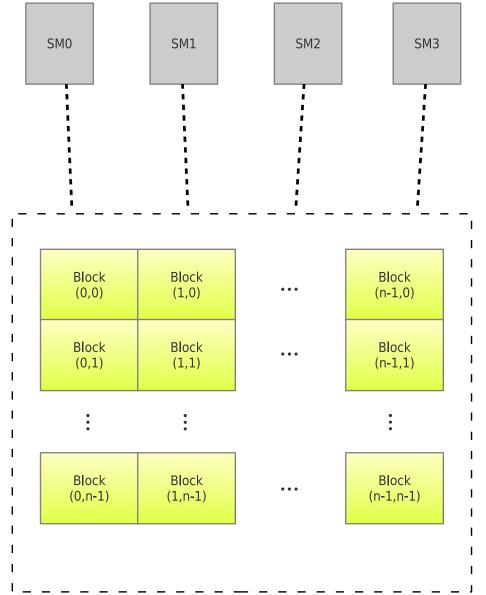

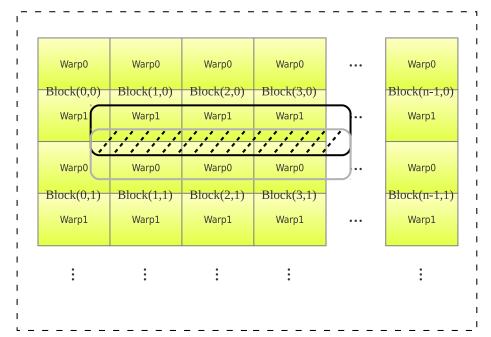

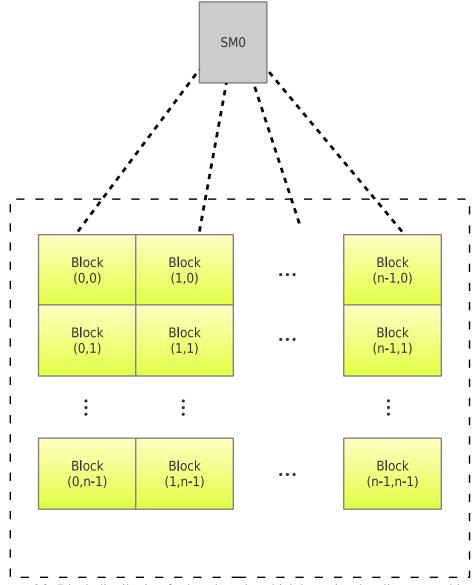

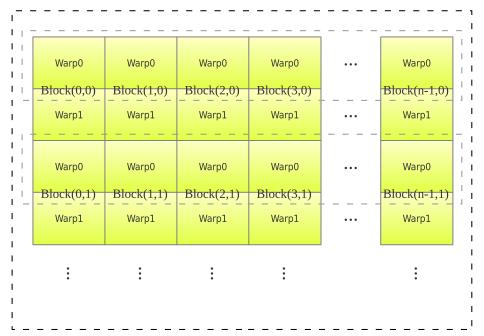

| 6.2  | Block scheduling inside GPU. Adjacent blocks are assigned to different SMs in               | 71  |

| ()   | round-robin fashion.                                                                        | 71  |

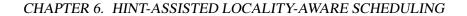

| 6.3  | High degree of spatial locality across adjacent blocks. Multiple cache line are shared.     | 73  |

| 6.4  | High degree of spatial locality across adjacent blocks. Boundary cache line are shared.     | 74  |

| 6.5  | Low-Mid degree of spatial locality across adjacent blocks. Some data are shared.            | - 4 |

|      | Code sample from HS benchmark.                                                              | 74  |

| 6.6  | Kernel launch using official CUDA API.                                                      | 75  |

| 6.7  | Kernel launch using our extended CUDA API.                                                  | 75  |

| 6.8  | Block distribution for benchmarks which have data locality among blocks                     | 77  |

| 6.9  | Warp scheduling for workloads which have multiple cache lines shared among blocks.          | 78  |

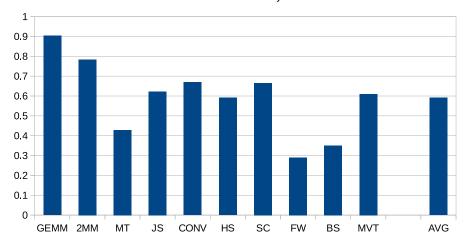

| 6.10 |                                                                                             |     |

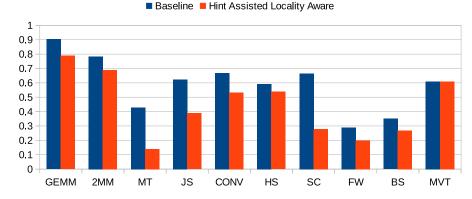

|      | model                                                                                       | 80  |

| 6.1  | Percentage of MSHRs allocated for duplicated cache lines in every 2000 cycles,              |     |

|      | relative to the baseline model.                                                             | 82  |

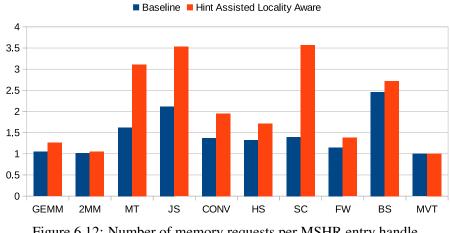

| 6.12 | 2 Number of memory requests per MSHR entry handle                                           | 82  |

# **List of Tables**

| 2.1 | Comparison between recent 5 different NVIDIA GPU architectures | 13 |

|-----|----------------------------------------------------------------|----|

| 2.2 | Comparison between the 5 most recent NVIDIA SM architectures   | 13 |

| 4.1 | Baseline GPU configurations                                    | 38 |

| 4.2 | List of CUDA benchmarks used for evaluation                    | 39 |

| 5.1 | List of benchmark applications                                 | 61 |

| 5.2 | Baseline GPU model configurations                              | 62 |

| 5.3 | List of benchmark applications                                 | 67 |

| 6.1 | Hint encoding                                                  | 76 |

| 6.2 | List of benchmark applications                                 | 79 |

| 6.3 | Simulated GPU configuration.                                   | 79 |

## Acknowledgments

I would like to dedicate this thesis to my parents. Without their unlimited support and encouragement during every single step of this journey, it would not have been possible for me to write this dissertation.

I am thankful to my colleagues at the NUCAR group, especially Leiming Yu, Xiang Gong, Zhongliang Chen, Shi Dong, Rafael Ubal Tena, Yifan Sun, and Julian Gutierrez. Thank you for all the wisdom you shared and the generous help you offered during my study. I would also like to thank my Ph.D. committee members, Dr. Ningfang Mi and Dr. Rafael Ubal, for providing me valuable ideas and constructive feedback on this dissertation.

Finally, I would like to express my deepest gratitude to my advisor, Dr. David Kaeli, for his constant support and guidance. His optimism and positive attitude always inspired me a lot and helped me overcome obstacles during my studies.

## Abstract

### Hint-Assisted Scheduling on Modern GPUs

by

Xun Gong

Doctor of Philosophy in Electrical and Computer Engineering Northeastern University, April 2020 Dr. David Kaeli, Advisor

Graphics Processing Units (GPUs) have become an attractive platform for accelerating challenging applications on a range of platforms, from High-Performance Computing (HPC) to full-featured smartphones. They can overcome computational barriers in a wide range of data-parallel kernels. GPUs hide pipeline stalls and memory latency by utilizing efficient thread preemption. As throughput-oriented processors, GPUs provide tremendous processing power by executing a massive number of threads in parallel. However, long memory latencies and limited throughput are still major bottlenecks in GPU applications. Although the cache hierarchy helps to reduce the memory system pressure, the massive thread-level parallel in GPU applications often causes cache contention. Given the demands on the memory hierarchy due to the growth in the number of compute cores on-chip, hiding memory stalls has become increasingly challenging.

Prior studies have explored a smarter warp scheduler to help GPU achieve peak performance, alleviating the stalls caused by long memory latencies. Most of these efforts have explored hardware-based warp schedulers solutions. hardware approach. In this thesis we take a different approach, developing a hardware/software co-designed warp scheduling strategy. Our scheduler selects independent instructions that are in the shadow of a long latency memory operation and executes them out-of-order when all warps are stalled due to memory system saturation. By introducing software-based scheduling hints provided by the programmer or compiler, our scheduler will make smarter scheduling decisions that will improve GPU performance.

To properly study the benefits of our novel hint-assisted warp scheduler, we need an accurate GPU simulation framework that supports GPU timing simulation. We have develop a cycle-accurate simulation framework that supports native execution of CUDA programs at the SASS (the GPU binary) level for the NVIDIA Kepler architecture. We have also developed a customized CUDA driver and runtime APIs, as well as GPU drivers to support simulation.

## **Chapter 1**

## Introduction

Over the past four decades, successive generations of microprocessors have been able to achieve faster clock speeds by exploiting Moore's Law, following the trend of CMOS scaling. Unfortunately, the top speed for today's microprocessors has peaked due to the exponential growth in power density of a single chip, commonly referred to as the *power wall*. Because of this trend, we have seen major shifts in processor architecture design over the past decade. Instead of continually scaling the clock speed of a single core central processing unit (CPU), multi-core architectures now dominate the commodity CPU market, dominated by ARM, Intel and AMD.

Given the rapid growth of scientific and engineering applications, where our inability to process massive datasets efficiently limits the rate of discovery, we need to move beyond current CPUbased platforms. Emerging applications include deep learning, autonomous navigation, computational chemistry, weather/climate modeling, and artificial intelligence for public good [43]. Faced with exponential growth in terms of the scale of the data to be processed, the performance gains of multi-core CPUs can not begin to meet the computational demands of these workloads.

Many researchers and industry leaders have proposed moving to heterogeneous system designs, where special-purpose accelerators, including graphic processing units (GPUs) and tensor processing units (TPUs) can work together with a multi-core CPU to offload compute intensive workload.

### **1.1 Growth of the GPU Market**

GPUs have been used to accelerate a wide range of general-purpose applications. The range of applications include high performance computing (HPC) to full-feature smart phones. More than 128 systems appearing in the 2018 TOP500 of the fatest supercomputers in the world are

equipped with AMD and NVIDIA GPUs as accelerators. GPUs have thousands of processing cores on chip, making them the platform of choice for accelerating dense matrix operations, neural network training and machine learning algorithms, as well as many other applications.

GPUs were originally designed render 3D graphics, though they have emerged to be both outstanding rendering engines for the gaming market, and high performance accelerators for a wide range of markets. Unlike many CPU applications, graphics workloads are much more sensitive to the overall throughput versus single-thread performance. As a result, GPUs are designed to be throughput sensitive, versus CPUs, which are latency sensitive.

To take full advantage of the massive parallel processing power of a GPU, Nvidia released its Compute Unified Device Architecture (CUDA) [48] development framework in 2007, the earliest widely used programming model for GPU compute applications. Two years later, Open Computing Language (OpenCL) [38] was developed and was widely supported by industry leaders including Apple, Intel and AMD. Compared to CUDA, a key feature of OpenCL is portability, supported by a variety of heterogeneous platforms such as digital signal processors (DSPs), field-programmable gate arrays (FPGAs) and GPUs.

In addition to CUDA and OpenCL programming frameworks, additional APIs and programming models have been developed to support general purpose computing on GPUs (GPGPU). The DirectCompute API [41] was developed by Microsoft to support GPU compute applications on Microsoft Windows Vista, Windows 7 and later versions. DirectCompute is part of Microsoft DirectX APIs and was initially released with DirectX 11 [32]. Nvidia worked with The Portland Group (PGI) to develop a CUDA Fortran Compiler which supports Fortran compilation on Nvidia's CUDA-enabled GPUs. This support was released in 2010 and now supports Linux, Windows and MacOS. OpenACC [73] is a directive-based programming model developed by Cray, CAPS, PGI and Nvidia. It is designed to provide a simple yet powerful approach for parallel GPU compute programming without significant programming effort.

In addition, GPU-accelerated libraries have been developed to provide programmers with highly optimized implementations of commonly used algorithms to speed up their development. GPU-accelerated libraries for signal processing, linear algebra, image and video processing include: cuFFT, cuBLAS and cuRAND [44]. These libraries are widely used in compute-intensive applications supporting a acceleration across a range of fields including computational chemistry, modecular dynamics and signal processing.

Given the growing support for GPU compute, researchers have muliple choices on the best way to accelerate their application using a GPU. Figure 1.1 shows three commonly used methods to accelerate applications on a GPU. The first leverages accelerated libraries, commonly referred to

Figure 1.1: Different ways to accelerate demanding applications.

as *drop-in acceleration*, where programmers use libraries to execute parallel computing functions without in-depth knowledge of GPU programming[44].

Programmers can utilize compiler directives, a strategy supported on OpenACC [73]. This provides programmers with a easy way to develop applications that maximize performance and power efficiency benefits of heterogeneous system. Compared to parallel programming languages such as CUDA [48] and OpenCL [38], compiler directives are much easier for people to learn. Developers can write their algorithms sequentially and introduce directives to exploit any parallelism present in the algorithm. The programmer gives the compiler hints to turn on parallelism.

Parallel programming languages such as OpenCL [38] and CUDA [48], provide a third approach to accelerating applications with a GPU. Many times it can be challenging to implement a high-performance application in a parallel language. The major benefits of using OpenCL and CUDA is that, equipped with low-level APIs provided by GPU vendors, programmers have more control over the code and can maximize performance across different architectures.

## **1.2 GPU Computing Model**

CPUs and GPUs represent two different design philosophies when it comes to architecture. CPUs are latency-oriented architectures that use large caches, branch prediction and complicated control logic to avoid stalls during execution. In contrast, GPUs are throughput-oriented systems that execute arithmetic operations and memory accesses concurrently on many data elements. GPUs do not provide complicated control flow logic. Instead, the GPU architecture is optimized to hide latency by providing massive parallelism and fast thread switching.

GPUs are designed to work as CPU co-processors to accelerate computation. The GPU is used to offload highly parallel and time consuming computation from the CPU, freeing up the CPU to process the remainder of the application. To achieve massive parallelism, GPUs adopt a Single Instruction Multiple Thread (SIMT) [31] programming model. To make best use of this programming model, today's GPUs are supported by a number of programming frameworks including OpenCL [38], CUDA [48] and HSA [27]. In this thesis, we will be targeting CUDA as run on an Nvidia GPU, so will use CUDA terminology.

A instances of a CUDA kernel is called a *thread*. Functions executed on a CUDA device are called kernels, which are organized in *thread blocks*. Multiple thread blocks are combined to for a *grid* of threads. When a kernel is called, N copies of the kernel are executed in parallel by N different CUDA threads. The threads executing the same instruction are grouped into a fixed sized batch, called a warp (NVIDIA) or a wavefront (AMD). All threads in the same warp share the same program counter and execute the same instruction.

## **1.3 Resource Underutilization**

To achieve double-digit speedups on a variety of applications, GPUs exploit Thread-Level Parallelism (TLP). Parallelism must be exposed by the programmer using one of two different approaches. Recall that GPUs adopt a SIMT [31] execution model. A warp of 32 threads are grouped to execute together, similar to an OpenCL wavefront. They execute the same instruction on multiple execution lanes. Second, GPUs execute many warps concurrently on a single processing unit. When one warp is stalled, the warp can be preempted by the warp scheduler, allowing a new warp to execute. A large portion of GPU die area is dedicated to execution units to support a high degree of concurrency. Execution lanes on a GPU use in-order processing pipelines and do not perform branch prediction. A hardware scheduler can hide latencies associated a blocked thread by swapping threads. Threads can get blocked due to data dependencies and branch divergence. The impacts of these disruptions can be reduced or avoided by swapping computation to non-blocked warps.

However, even equipped with the mechanisms available that are designed to hide latencies, GPU resources remain frequently underutilized. For example, when a memory-intensive workload needs to load a block of data from off-chip DRAM, many threads compete for the available memory bandwidth to DRAM, saturating the memory interconnect, stalling all warps until memory dependencies can be resolved. In this thesis, we propose and evaluate different techniques to utilize GPU resources more efficiently, especially for memory intensive workloads.

## **1.4** Motivation of this thesis

The warp scheduler on modern GPUs can swap warps that are stalled, when faced with a data dependency. However, one of the biggest challenges which prevents GPUs to achieve peak performance is the effective utilization of computation resources. When a memory intensive workload needs to load a block of data from off-chip DRAM, many threads compete for DRAM bandwith, saturating the memory interconnect. When we encounter this situation, a new memory request cannot be serviced until the older memory requests complete. Since memory requests are not pipelined, the warp scheduler can not hide most of the latency associated with these memory operations by swapping in runnable warps. As a result, warps will stall on instructions that depend on long latency memory instructions. The number of active warps will decrease as more warps hit the stall point. Eventually, all the warps will stall and wait until the long latency memory load is resolved.

Figure 1.2 shows the breakdown of scheduling cycles for 6 workloads. The portion of the stacked bars identified as Issued denotes that at least one warp in the GPU is eligible to be issued. The Long Latency Stall portion shows that all warps in GPU are stalled due to a long latency memory operation. Mixed Stall denotes that no warps can be issued in that cycle, which may be due to a variety of reasons (e.g., there is no available instruction in the fetch buffer, the pipeline is busy, a data dependency has occurred, etc.). In Figure 1.2, we can see that the fraction of long latency operation stalls in 4 out of 6 of our benchmarks is around, or more than, 25%. We classify these applications as memory intensive benchmarks. In three of these workloads, long latency stalls dominate over 30% of the execution. We classify the other two workloads as non-memory intensive, since less than 10% of their execution is dominated by long latency stalls.

For both memory intensive and non-memory intensive benchmarks, a large percentage of the total execution cycles (more than 50%) are spent waiting on different kinds of stalls. This trend is especially noticable in the memory intensive benchmarks, where the total stall cycles of some benchmarks consume more than 70% of the total cycles. How can we better utilize the GPU computing resources? We need to reduce the impact of long latency operation stall by leveraging

Figure 1.2: Breakdown of scheduling cycles.

The warp scheduler present in a GPUs Streaming Multiprocessor (SM) plays a pivotal role in achieving high performance for GPU applications, specifically by distributing hardware resources to different warps when the GPU stalls. Previous studies [28, 40, 37, 14, 30] developed different warp scheduling algorithms to improve GPU performance. However, all of these efforts focused on a pure hardware-based approach for the warp scheduler. Designing an effective warp scheduler in a hardware/software co-design approach has not been studied extensively on GPUs. In this thesis, we pursue an approach uses both hardware and software to increase GPU resource utilization and improve overall performance. We propose the following mechanisms:

- 1. Execute instructions in a selective out-of-order fashion in order to keep GPU computing resource busy whenever there is a long latency memory stall.

- 2. Assign thread blocks which have high spatial locality to execute on the same Streaming Multiprocessor utilizing better warp scheduling to co-schedule warps that use the same data.

## 1.5 Challenges

#### **1.5.1 Lack of GPU Simulation Framework**

Modern computer architecture continue to grow in complexity, making them more challenging to evaluate. Simulation frameworks provide researchers and computer architects the ability to quantitatively evaluate architectural designs and evaluate design trade-offs. In general, architectural simulators [7] can be divided into two categories: i.) functional simulators and ii.) timing simulators. Functional simulators can accurately execute a program, simulating the functional aspects of the underlying architecture, but provide no timing information.

Timing simulators implement all of the hardware components and microarchitectural details, providing cycle-accurate timing information. Timing simulators capture detailed interactions between the compute pipelines and memory system. The typically take much longer time to execute as compared to a functional simulator, since a timing simulation must provide both functional accuracy, as well as timing accuracy.

To better analyze GPU performance and program behaviour, and to consider both hardware and software enhancements, a cycle-accurate GPU simulator is needed. However, only a limited number of open-source cycle-based GPU simulators have been developed in the academic research community. Prior to this thesis, there was no cycle-accurate open-source simulation framework that runs NVIDIA SASS-level (i.e., the executable binary level) executino. One key reason for this is that NVIDIA is highly proprietary about their instruction set architecture (ISA), driver information and architectural details. The lack of public information dramatically increases the burden on researchers that want to study GPU architecture. Developing such a simulator requires a significant investment in time and reverse-engineering to work out each instruction implementation, hardware timings, driver APIs and other hardware details.

This leads to our first challenge on developing a more advanced warp scheduling algorithm on GPU. Researchers cannot study GPU performance and analyze architectural details because of the lack of a simulation framework. To address this issue, in this thesis, we present Multi2Sim Kepler [16], a GPU simulation framework that support Nvidia SASS code execution. Equipped with this simulator, we can evaluate performance and tradeoffs when targeting the Nvidia Kepler architecture [46]. Multi2Sim [67] is a framework developed by Ubal et al., that can simulate both a number of CPU and GPU architectures. The work developed in this thesis supports a new ISA (Kepler) and a new programming framework (CUDA).

#### 1.5.2 Lack of Control Logic

The performance of modern processors still suffers from the memory wall [35] and branch penalties. One way to alleviate this problem is to introduce instruction hints to increase the cache hit rate and decrease the branch misprediction rate. In some power-efficient processor models, architects elected to remove the hardware branch predictor and use a software branch hint to recover the lost performance. This was realized in the IBM's Cell Synergistic Processing Units [21]. When using software branch hints, hint instructions are inserted in the application, specifying that the branch instructions located at a specific PC address will jump to a specific target address. The processor will start to speculatively execute target instructions after executing a hint instruction, when the specified branch instruction is still in flight.

Compared with a CPU, a GPU is power-efficient and throughput-oriented processor. GPUs do not implement complicated control logic, such as branch predictor or reservation stations. Whenever a warp encounters a stall due to a data or control dependency, the warp has to wait until the dependency is resolved in order before continuing execution. Instructions cannot execute in out-of-order to bybass the stall and hide the performance penalty associated with the dependency. Since there are tens of thousands of threads running on the GPU simultaneous, it is impossible to add complex control logic while still maintaining the power efficiency on the GPU. This leads to our second challenge, GPUs lack sophisticated control logic to allow a warp to remain active when encountering long latency stalls.

To address this issue, our approach for GPUs is inspired by previous work applied to CPUs. We can introduce hints during complication to distribute thread blocks and schedule warps to better utilize GPU computing resources and improve application performance. We provide a compiler pass to analyze and mark the instructions that are independent of long latency memory instructions. These instructions are in the shadow of memory instructions. We design a compiler-generated hint that encodes this information and embeds it into the instruction stream. Based on these hints, the warp scheduler can choose to issue independent instructions and execute them out-of-order when all warps are stalled due to memory system saturation. The goal is to keep GPU resource utilization high, while allowing programs to execute past dependencies. Unlike CPUs, which use techniques such as reservation stations [66] and reorder buffers [26] to support out-of-order execution, it would be costly to replicate hardware components on a GPU, given that there could be hundreds of warps executing concurrently. Instead, Hint-Assisted Warp Scheduler (HAWS) uses hints provided by the compiler to schedule and execute instructions in a selective, out-of-order, fashion. HAWS executes non-speculative instructions and schedules warps based on the scheduling algorithm we choose (round-robin, GTO, etc.). When all warps stall because of long latency memory operations, HAWS

triggers our hint-assisted scheduler, which will only fetch and execute the instructions that are independent from the long latency memory operation. We describe the details in Chapter 5.

#### **1.5.3** Intensive Memory Contention in GPUs

As discussed earlier in this thesis, a GPU is only partially tolerant of memory delays. Whenever a warp generates a memory request, other warps also likely make memory requests in close time proximity. When thousands of memory requests compete for the limited memory bandwidth, this will increase the time required to fulfill those requests. GPU memory resources are not designed to handle this scale of parallelism in the memory system. This leads to our third challenge, addressing he need to achieve high resource utilization on a GPU.

To alleviate this problem, we have designed scheduling hints to exploit the spatial locality among different warps. For workloads such as matrix multiplication, which is a commonly used operation in machine learning and scientific applications, the memory reference pattern exhibits high spatial locality, especially across adjacent thread blocks and warps. We propose and design additional scheduling hints to provide detailed information which can be used by a warp scheduler to exploit any spatial locality inherent in a workload. For the adjacent thread blocks, the CTA scheduler will assign them to the same SM, versus distributing them to different SMs, in a round-robin fashion. For the warps which share high spatial locality, but are in different thread blocks, the warp scheduler will assign them to the same group to execute together according to the scheduling hints. This scheme can make better use of the available memory bandwidth. The details of this design are presented in Chapter 6.

### **1.6** Contributions of This Thesis

In this thesis, we pursue a hardware/software co-design approach to design a novelty warp scheduler to improve the utilization of GPU hardware resources and reduce memory contention. The key contributions are summarized below:

- We reverse engineer the Kepler GPU ISA, microarchitecture, memory hierarchy, as well as driver and runtime information.

- We identify and analyze the importance of running GPU simulation at the native SASS level and evaluate the difference between simulating at a higher intermediate language (PTX) level versus working at a SASS binary level.

- We develop a cycle-based GPU simulator based on the Nvidia Kepler architecture and demonstrate its accuracy as compared to execution on the real GPU hardware.

- Leveraging our simulator, we characterize a rich set of workloads to identify the sources of GPU resource underutilization.

- We implement a hinted-assisted warp scheduler in our simulation framework and show how it can improve GPU performance. We design a novel hint encoding format to embed the hint in the SASS instructions. We have proposed a novel warp scheduling algorithm named HAWS, which uses GPU resources more efficiently and can hide long latency memory operations.

- We analyze a broad set of benchmarks and find high degrees of spatial locality across adjacent thread blocks in some benchmarks. We classify these benchmarks and demonstrate we can better utilize spatial locality and reduce memory pressure using better thread block scheduling techniques.

- We develop a novel hint-assisted locality-aware warp scheduler to utilize this pattern and improve application performance. For different classifications of benchmarks, we design scheduling hints to group those warps and execute them together to fully enjoy the benefits of spatial locality and reduce memory bandwidth demands.

## **1.7 Organization of Thesis**

The rest of this thesis is organized as follows. Chapter 2 presents background information on general-purpose computing on GPUs, GPU architecture, and details on the GPU memory hierarchy and performance. Chapter 3 presents prior work that addresses how to hide main memory access latency to improve GPU application performance. We describe the details of our simulation framework in Chapter 4. The hint-assisted warp scheduler is described in Chapter 5. We present hint-assisted locality-aware scheduling in Chapter 6. Finally, in Chapter 7, we conclude the thesis and discuss directions for future work on this topic.

## **Chapter 2**

## Background

## 2.1 History of GPU computing

Computation on a GPU was first introduced by providing programmable shaders. In 2001, both OpenGL [74] and DirectX [32] added support for programmable shaders to give game developers and designers more space to create custom graphics effects. Graphics artists can now render their graphics by writing programs that execute directly on the GPU. Soon after, researchers discovered that GPUs are a good fit for many classes of data-parallel high performance computations in graphics applications, which motivated research into accelerating non-graphics applications on GPUs. At the beginning of GPU computing, a variety of high performance computing algorithms were ported from a CPU to a GPU, using high-level shading languages such as OpenGL and DirectX. Applications, including linear algebra, financial modeling, database queries, and image processing, have all achieved speedup when mapped to a GPU.

However, porting these general purpose applications from CPUs to GPUs, when leveraging a graphics programming language, can be very timing consuming and complicated for multiple reasons. First, computational algorithms need to be expressed in terms of textures, vertex coordinates, and shader programs, significantly increasing programming complexity. Second, programmers needed to have both a comprehensive knowledge of the GPU architecture and graphics APIs. Furthermore, the lack of double-precision and limitations on random memory access support restricted the type of applications that could be run on GPU.

To address these issues, GPU vendors started to explore general purpose computing on GPUs. CUDA [48] and OpenCL [38] were introduced by Nvidia and the Khronos Group in late 2000s. With the introduction of new general purpose programming models, programmers were no longer tied to using a graphics APIs, enabling them to focus on application performance and shorter

development cycles.

Researchers from different domains started to use GPUs to accelerate applications. Medical imaging was one of the first applications to take advantage of a GPU's massive compute power. Mueller et.al [75] implemented cone-beam computed tomography(CBCT) algorithm in CUDA. They achieved a 500X speedup over the CPU implementation by using an NVIDIA GTX 8800 GPU. Sorensen et.al [64] demonstrated the use of a GPU in signal processing. They implemented a parallel Nonequi-spaced Fast Fourier Rransform (NFFT) on GPU, achieving a 85X speedup versus running on a state-of-the-art CPU. In bioinformatics, Schatz et.al [61] designed MUMmerGPU, an open-source high-throughput parallel pairwise local sequence alignment program. They achieved 10-fold speedup over a highly optimized serial CPU version of sequence alignment code.

## 2.2 GPU Evolution

As problem sizes have continued to grow, GPU vendors keep introducing more powerful architectures to fulfill the growing demands for both computation and energy efficiency. They integrate more transistors in a single die area to make GPUs have more computing power. Table 2.1 shows the parameters of the most recent five generations of NVIDIA GPUs. From Fermi [45] architecture to Volta [51] architecture, for a single GPU, we can see that the number of singleprecision float point (FP32) CUDA cores has greatly increased, as well as double precision float point (FP64) CUDA cores, peak FP32 trillion floating-point operations per second (TFLOPS), and the total number of transistors. From Fermi to Kepler [46], the most significant upgrade we the number of FP32 CUDA cores per GPU, which is increased to 2880 [46], 6.4 times the amount in Fermi. The reason NVIDIA has managed to integrate so many cores onto a single die is that Kepler is the first chip produced on a smaller 28 nm process as compared to the 40 nm process in Fermi. Maxwell [47] adopted the same 28 nm process as did Kepler, so there is a limited increase in FP32 CUDA cores per GPU from Kepler to Maxwell. From Maxwell to Volta, the number of total transistors per GPU grew. The total number of transistors in Pascal [50] is almost double that in Maxwell. In Volta, this number is increased by 40% compared to Pascal, reaching 21.1 billion per GPU. The number of cores in the GV100 [51] almost doubles that in the GK180. As shown in the table, the peak FP32 TFLOPS for the GV100 is 2.6 times as high as for the GK180.

In the Fermi architecture, each SM contains 32 FP32 CUDA cores [45], which is 4X over the previous generation GT200. There are two warp schedulers, and each of them feeding the dispatch unit. Fermi's dual warp scheduler selects instructions from two different warps each cycle and dispatches one instruction from each warp to a group of 16 FP32 CUDA cores, 16 load/store

| Architecture          | Fermi | Kepler | Maxwell | Pascal | Volta |

|-----------------------|-------|--------|---------|--------|-------|

| Release year          | 2009  | 2012   | 2014    | 2016   | 2017  |

| Model                 | GF100 | GK180  | GM200   | GP100  | GV100 |

| FP32 CUDA Cores / GPU | 448   | 2880   | 3072    | 3584   | 5120  |

| FP64 CUDA Cores / GPU | N/A   | 960    | 96      | 1792   | 2560  |

| Peak FP32 TFLOPS      | 1.03  | 6      | 6.8     | 10.6   | 15.7  |

| Transistors (billion) | 3     | 7.1    | 8       | 15.3   | 21.1  |

| GPU Die Size $(mm^2)$ | 529   | 551    | 601     | 610    | 815   |

Table 2.1: Comparison between recent 5 different NVIDIA GPU architectures.

| Architecture                 | Fermi | Kepler | Maxwell | Pascal | Volta |

|------------------------------|-------|--------|---------|--------|-------|

| Release year                 | 2009  | 2012   | 2014    | 2016   | 2017  |

| FP32 CUDA Cores / SM         | 32    | 192    | 128     | 64     | 64    |

| FP64 CUDA Cores / SM         | NA    | 64     | 4       | 32     | 32    |

| Tensore Cores / SM           | NA    | NA     | NA      | NA     | 8     |

| Register File size / SM (KB) | 128   | 256    | 256     | 256    | 256   |

| Warp Schedulers / SM         | 2     | 4      | 4       | 4      | 4     |

| Dispatch Units / SM          | 2     | 8      | 8       | 8      | 4     |

| Load / Store Units / SM      | 16    | 32     | 32      | 32     | 32    |

| Special Function Units / SM  | 4     | 32     | 32      | 32     | 4     |

Table 2.2: Comparison between the 5 most recent NVIDIA SM architectures.

units, or 4 special functional units (SFUs). It takes two consecutive cycles to issue each FP32 instruction since 32 threads are running on 16 FP32 CUDA cores. In Kepler, each SM has 192 FP32 CUDA cores and four warp schedulers, which allows four warps can be issued every cycle [46]. Each warp scheduler is grouped with two dispatch units, issuing two independent instructions from the same warp simultaneously. Unlike Fermi, each FP32 instruction is executed on 32 cores, so it only takes one cycle to issue. SMs in Kepler also features FP64 CUDA cores to improve double precision performance. In Maxwell, NVIDIA integrated several improvements to further reduce redundant scheduling decisions to enhance power efficiency. Compared to the 192 FP32 CUDA cores per SM (a non power of 2 organization design) in Kepler, each SM in the Maxwell features 128 FP32 CUDA cores. They are partitioned into four different 32 FP32 CUDA core processing blocks, each has dedicated scheduling resources including a warp scheduler and dispatch unit [47]. In Pascal, each SM is integrated with 64 FP32 CUDA cores, half the total number of FP32 CUDA cores as Maxwell. The number of FP64 CUDA cores in Pascal is increased to 32 per SM from 4 in Maxwell, significantly increasing the chip's ability to handle double-precision arithmetic, which is the core part of many HPC applications such as artificial intelligence, linear algebra, and computational chemistry. Similar to Pascal, the SM in Volta also features 64 FP32 CUDA cores and 32 FP64 CUDA cores.

However, SM in Volta adopts a different partitioning method to improve the overall performance and resource utilization. In Pascal, the SM is separated into two processing blocks while the SM in Volta is partitioned into four processing blocks. Another significicant update in Volta is that each SM is equipped with eight tensor cores [51], where each can perform 64 floating point FMA operations per clock cycle. Tensor cores deliver up to 12X higher peak TFLOPS in FP32 operations and 6X higher peak TFLOPS in standard FP16 operations, as compared to Pascal P100.

## 2.3 SIMT Programming Model

The Single Instruction Multiple Thread (SIMT) programming model is the execution model used in modern GPUs and is supported by several programming frameworks including OpenCL [38], CUDA [48] and HSA [27]. In this thesis, we will be targeting CUDA as run on an NVIDIA GPU, so will use CUDA terminology.

Figure 2.1 provides an overview of the execution element hierarchy defined in CUDA. Functions executed on a CUDA device are called *kernels*, which specify a *grid*. When a kernel is called, N copies of the kernel are executed in parallel by N different CUDA threads. An instance of a CUDA kernel is called a *thread*. A *warp* of 32 threads is grouped to run together, similar to an OpenCL *wavefront*. All threads in the same warp share the same program counter and execute the same instruction.

A *cooperative thread array* (CTA) or thread block consists of several warps. All threads in the same CTA have two basic properties: i.) within a single CTA, threads can perform efficient synchronization operations, and ii.) threads within the same CTA can share data through a low-latency shared memory. All CTAs from the same grid share a common global memory.

Figure 2.1: The CUDA Programming Model.

Figure 2.2 presents an overview of a typical GPU architecture. The GPU organization includes a giga-thread engine (thread block scheduler), a collection of Streaming Multiprocessors (SMs) and a memory hierarchy. The thread block scheduler processes the grid and maps waiting thread blocks onto the available SMs. Once a thread block is assigned to an SM, it remains in the SM until its execution completes. Resources, such as registers and shared memory, are not freed until the thread block finishes execution. Multiple thread blocks can be assigned to a single SM if there are available resources.

Figure 2.2: A typical GPU architecture.

CUDA defines the concept of a warp as a group of 32 threads executing in SIMT fashion. Each instruction is executed concurrently by every thread comprising a warp, although each thread has its data for computation. This model simplifies the instruction fetch hardware by implementing a

common front-end for a whole warp. On every cycle, the SMs front-end fetches instructions from instruction memory for the different warps and sends them to the appropriate execution unit. For example, in the NVIDIA Kepler microarchitecture, each SM front-end features four warp schedulers and eight instruction dispatch units, allowing four warps to be issued and executed concurrently. When a warp is stalled due to a long latency memory operation or other reasons, the warp scheduler can quickly switch and issue another warp to hide the latency.

As hundreds of thousands of threads are launched on GPUs, the scheduling of the threads can have a significant impact on the overall performance. To increase the performance, people need to consider how to distribute the thread blocks to SMs and schedule the warps to utilize the hardware resources better. An efficient warp scheduler can either improve resource utilization or hide the impact of long memory latency operations, keeping the GPU computing resources as busy as they can.

### 2.4 GPU Architecture

#### 2.4.1 Steaming Multiprocessor Architecuture

A GPU is comprised of multiple SMs. During execution time, an SM can have one or more thread blocks allocated. These thread blocks are split into warps, which are assigned to SMs that execute threads. SMs are identical, with the major units and organization provided in described in Chapter 2.3. The warp scheduler is responsible for picking up available warps from the warp pool to execute every cycle. Since hundreds of warps are running on the same SM simultaneously, effective scheduling should try to hide memory latency, improving application performance. On every cycle, the SM front-end fetches instructions from instruction memory for the different warps and sends them to the processing cores. Each SM has tens or hundreds of processing cores (also called CUDA cores by NVIDIA). For example, in the Kepler architecture, there are 64 cores per SM. In the Maxwell architecture, there are 128 cores per SM. There are several types of processing cores, such as single-precision units (SPU/FP32), double-precision units (DPU/FP64), and SFUs. Each type of unit executes the corresponding arithmetic operations. The load/store units service all memory-related instructions.

#### 2.4.2 GPU Memory Hierarchy

The GPU memory hierarchy is a bit complicated since it includes shared memory, texture memory and constant memory, each with different characteristics including access latency, access scope and read-write access. By properly leveraging the GPU memory hierarchy, the programmer

Figure 2.3: A typical SM architecture.

can reap better performance. It become critical for GPU programmers to understand the GPU's memory hierarchy in order to achieve better performance. Previous studies have explore how best to leverage the GPU's memory hierarchy [65], [60], [77], [8]. For example, on a GeForce 8800 GTX GPU, magnetic resonance imaging (MRI) can achieve 18.6 GFLOPS by using constant memory to reduce the average memory access time. Compared with the global memory version, utilizing

constant memory can provide a 4X speedup [65]. Zhao et al. implemented G-BLASTN, which can achieve a 14.8x speedup, just by balancing shared and texture memory usage, as compared with the sequential NCBI-BLAST [77].

The on-chip GPU memory hierarchy is illustrated in Chapter 2.3. The hierarchy consists of a register file, L1 cache, shared memory, texture cache, and constant cache. The register file provides the fastest access in the memory hierarchy, which is private to each CUDA thread. In ithe Fermi architecture, the number of registers that can be accessed by a CUDA thread is 63 [45]. This number has been quadrupled in Kepler architecture, allowing each thread to access up to 255 registers [46] and is kept the same in the latest Volta architecture [51]. The number of registers used per thread is determined by the programmer and the compiler for GPUs. Since the total size of the register file is limited, the fewer registers each thread uses, the more threads can be launched simultaneously in a single SM.

Shared memory is another critical part of the GPU memory hierarchy. Since it is on-chip memory, shared memory is much faster and has much lower access latency as compared to the global memory. Shared memory is allocated per thread block, so any data stored in shared memory is visible to all threads in the same block. In other words, a thread can access data in shared memory, which is loaded by other threads from global memory if they are in the same thread block. To achieve high memory bandwidth, shared memory is separated into memory bank, allowing simultaneous memory accesses across different banks. When there are multiple memory accesses mapped to the same bank from different threads, the accesses will be serialized due to contention in the memory bank. An exception is when all threads in a warp access the same shared memory address. In this case, a broadcast will occur instead of serialized access, avoiding the penalty of bank contention.

The number of banks in shared memory is 16 for devices whose compute capability is 1.x. In this case, a shared memory request from a warp will be split into two consecutive cycles. For the Fermi architecture, the number of banks in shared memory is 32, which allows a warp to access shared memory within a single cycle. Starting with the Kepler architecture, programmers are allowed to use the CUDA API to configure the bank size to avoid shared memory bank conflicts. Also starting with the Kepler architecture, the on-chip memory in the SM can be partitioned between L1 cache and shared memory. Programmers can use the CUDA API to configure the shared memory size to improve the application performance.

The constant cache is a read-only cache for the SM to store data that does not change during kernel execution. Constant cache can broadcast the required data when all the threads in a warp access the same address, which reduces the required memory bandwidth significantly. Similar to constant cache, texture cache is also a read-only cache. NVIDIA initially designed texture memory

for graphics rendering pipelines. It is beneficial when the memory access pattern in the kernel exhibits high spatial locality. The data in texture memory is cached in texture cache, which can reduce a lot of memory traffic and improve the overall performance.

### 2.5 Warp Scheduling

#### 2.5.1 Scheduling Algorithms

Scheduling techniques play a vital role in improving GPU performance. For many GPU applications, hardware resources are not efficiently used, resulting in degradation of performance. One significant problem programmers try to address by using different scheduling techniques is to hide the impact of long latency memory instructions to improve overall performance. When there is a large number of memory requests over a short amount of time, memory bandwidth can become saturated, serializing subsequent accesses to memory. Additional warps will have to wait until the memory instructions are finished to resolve data dependencies, which results in low utilization of GPU computing resources.

Several previous studies focused on this problem by using different scheduling techniques. Narasiman et al. [40] introduced a two-level warp scheduler which separates warps into different groups, preventing them from reaching the same long latency instruction at the same time. This design allows the streaming multiprocessor to hide long latency operations by switching between different groups while ensuring memory locality within the same group. Jog et al. [19] presented OWL, a CTA-aware scheduler that uses data locality information to limit the number of CTAs in each SM and reduce cache contention.

Unlike previous work that leveraged pure hardware GPU scheduling techniques, in this thesis, we use a hardware/software co-design approach to deliver a novel warp scheduler which can improve GPU performance.

## **Chapter 3**

## **Related work**

### **3.1** Using Hinting in Microprocessors

Instruction hints have been present in modern microprocessors in previous designs. They have been used primarily for resolving branch mispredictions and cache misses in CPUs. The Intel Itanium 2 [36] ISA defined hint instructions that are used to provide the hardware early information about a future branch, and also direct the instruction prefetch engine to prefetch one or many L2 cache lines to increase cache hit rates.

Another popular example is the Synergistic Processing Unit (SPU) in the IBM Cell processor [21]. Jointly developed by Sony, Toshiba, and IBM, architects decided to remove the hardware branch predictor and use the software branch hinting to recover lost performance. Compared to the Intel Itanium, the Cell SPUs do not have any hardware branch predictor and rely solely on software branch hints to make the design more power efficient.

In the EPIC (Explicitly Parallel Instruction Computing) [62] ISA family, introduced by Hewlett Packard and Intel, the compiler performs direct cache placement and actively manages replacement policies through cache hints. The cache hints allow the compiler to have more control on cache behavior. The compiler can schedule instructions explicitly in parallel to hide long latency loads based on the true latency of instructions informed by the cache hints. The target cache hints are used to indicate the cache level at which the data will be kept after the instruction is executed.

Beyls et al. [6] proposed to generate cache hints from a reuse distance metric. Since the reuse distance indicates the cache behavior, irrespective of the cache size and associativity, it can be used for making caching decisions for all levels of cache hierarchy. Both static and dynamic approaches were proposed in this prior work. The static approach uses profiling to assign a cache hint to a memory instruction statically. The dynamic approach is based on an analytical model used

to select the most appropriate hint dynamically.

Wang et al. [72] developed an analytical model that predicts which data will be reused by using compiler hints. These hints are provided to improve replacement decisions in set-associative caches. Their work explores options for reducing cache misses by adopting compiler hints to improve replacement decisions.

On the GPU side, NVIDIA started to inject instruction hint starting from the Kepler architecture [46]. They insert instruction hint for every eight instructions to assist their hardware scheduler. But due to the proprietary nature of this information, we have not found documentation describing the details of these hints.

## 3.2 Warp Scheduling

Previous studies have shown that the warp scheduler plays an essential role in improving GPU performance. Lakshminarayana and Kim [28] evaluated different fetch and DRAM scheduling policies on the performance of GPU applications. They ran different combinations of fetch and DRAM scheduling policies on a series of benchmarks and showed that, for applications that execute symmetric instruction length per warp, a fairness based warp and DRAM access scheduling policy improves performance. For applications that have various instruction counts per warp, different applications show benefits with different combinations of fetch and DRAM policies.

Narasiman et al. [40] introduced a two-level warp scheduler which separates warps into different groups, preventing them from reaching the same long latency instruction at the same time. This design allows the SMs to hide long latency operations by switching between different groups, while ensuring memory locality within the same group. Compared with the baseline round-robin scheduling policy, they can achieve a 9.9% speedup on average.

Meng et al. [37] proposed Dynamic Warp Subdivision (DWS), which splits a warp into two warps in the presence of a branch divergence or memory divergence. This method allows an SM to interleave computation down different branch paths in order to hide memory latency. In addition, DWS allows the threads that hit in the cache to continue to execute aggressively, even if some of their peer wavefronts have encountered a miss (i.e., a memory divergence).

Gebhart et al. [14] demonstrated that a combination of two-level warp scheduling and register file caching techniques could provide power savings without losing performance for applications. Register file caching can replace accesses to the large main register file, using a smaller hardware structure, which saves energy. Combined with register file caching, a two-level warp scheduler can further reduce energy usage by limiting the temporary register cache resources to currently active

groups of threads. They showed that by using a 6-entry per thread register file cache, they could achieve a 36% reduction in terms of register file energy.

Lee et al. [30] proposed Criticality-Aware Warp Scheduling (CAWS) for GPU workloads, implementing a warp scheduling algorithm based on warp criticality. They showed that for specific workloads, such as breadth-first-search, the overall performance of the application is limited by the execution time of critical warps (the warps have a longer execution time). They identified the sources of criticality in warps and designed CAWS to balance the execution time of different warps in the same thread block. CAWS assigns priority to the critical warps, given them more opportunities to execute as compared with regular warps, maximizing the hardware resource utilization and reducing the overall execution time.

Lee et al. [29] proposed an alternative thread block scheduling designed to maximize GPU resource utilization. There are two main techniques they introduced. The first one is Lazy CTA Scheduling (LCS), which reduces the number of thread blocks allocated to an SM dynamically, avoiding performance degradation due to resource contention. The second technique they proposed is Block CTA Scheduler (BCS) that schedules adjacent CTAs to the same SM to improve spatial locality and improve performance. According to their report, they achieved an average of 16% speedup over the baseline GTO scheduler by combining LCS and BCS.

Rogers et al. proposed Variable Warp Sizing(VWS) scheduling [57], using a smaller warp size to execute when control flow and memory divergence occurs, improving the performance of divergent applications. VWS evolves the GPU into a more suitable computing device for irregular applications by adopting smaller warps to increase thread-level parallelism (TLP) and SIMD efficiency. VWS also improves energy efficiency by grouping the small warps to execute together, trying to build a MIMD-like computing model, but with SIMD model efficiency. According to their report, VWS can achieve a 35% performance improvement on divergent workloads.

## **3.3** Exploiting Thread Level Parallelism (TLP) on GPUs

Many warp scheduler studies have focused on choosing the right amount of TLP for the memory sub-system to avoid over-saturation, and to reduce latency. The Cache-Conscious Wavefront Scheduler (CCWS) proposed by Rogers et al. [58] preserves intra-wavefront locality by using additional hardware to adjust the amount of TLP per SM, keeping the L1 data cache from thrashing and maintaining intra-wavefront locality. They also introduced static wavefront limiting (SWL), which allows the programmer to set a limit on the number of active wavefronts per compute unit, during kernel launch. Based on their study, CCWS can provide a 24% performance improvement

over a round-robin scheduling policy across a set of cache-sensitive workloads.

Fung et al. [13] explored the impact of branch divergence on GPU performance and proposed dynamic warp formation (DWF). DWF attempts to mitigate control flow divergence by dynamically creating new warps when threads in the same warp that take different paths after branch instructions execution. They implemented the hardware required for DWF and achieved a 20.7% speedup on average, with an additional 4.7% area overhead.

Fung and Aamodt [12] proposed thread block compaction, a novel mechanism to improve TLP when divergence occurs. Threads within the same thread block are compacted into new warps when they encounter a divergent branch. The compacted warps synchronize again at the reconvergence point and resume in their original arrangements before divergence. Compared with their previous study on dynamic warp formation, thread block compaction ensures a sufficient number of threads are available at the divergent branch to be compacted into new warps. Their simulation results show they can obtain an overall 22% speedup over a per-warp reconvergence stack baseline when running divergent applications, with no additional performance penalty.

Vaidya et al. [68] proposed two compaction techniques: 1) Basic Cycle Compression (BCC), and 2) Swizzled Cycle Compression (SCC) which use idle SIMD lanes to execute consecutive instructions. BCC squeezes out cycles for other instructions in the execution pipeline when there are any a set of 4 aligned threads are inactive. SCC is an improvement over BCC. SCC combines the active unaligned threads to execute in consecutive lanes. Their evaluation results show that BCC and SCC can reduce execution cycles in divergent applications up to 42% (20% on average) on Intel Ivy Bridge GPUs.

Rhu et al. [56] introduced the Dual-Path execution model (DPE), a model which exploits intra-warp parallelism by interleaving the execution of different paths when divergence occurs in a warp. Unlike prior solutions to handling divergence, DPE does not require an extensive redesign of the microarchitectural components. Instead, DPE extends the stack to support two concurrent execution paths. Using a series of benchmarks, the authors found that dual-path execution either matches the performance of the baseline single-path stack architecture or outperforms single-path execution by 14.9% on average, and by over 30% in some cases.

Kayiran et al. [23] proposed a dynamic CTA scheduling technique (DYNCTA) that attempts to allocate the optimal number of CTAs per core based on application demands. Their work showed clearly that executing the maximum number of CTAs per core is not always the best solution to boost performance, due to high cache and memory contention. DYNCTA provides a 28% performance improvement, on average, as compared to the default CTA scheduler, where the maximum number of CTAs are executing on the SMs.

Yu et al. [76] presented a Stall-Aware Warp Scheduling (SAWS) policy, which dynamically optimizes the TLP according to pipeline stalls. SAWS can effectively improve pipeline efficiency by reducing structural hazards without introducing new data hazards. SAWS monitors the structural hazards for all executed instructions and adjusts the number of active warps dynamically according to the number of structural hazards. SAWS achieves a 14.7% performance improvement on average compared to round-robin scheduling.

Kloosterman et al. [25] proposed WarpPool to identify spatial locality between threads in multiple warps and merge their requests being sent to the L1 cache. This reduces the memory bandwidth usage and relieves the bottleneck between the load store unit and the L1 cache. WarpPool achieves a 38% speedup on memory throughput-limited kernels by increasing the throughput to the L1 by 8% and reducing the number of L1 misses by 23%.

Wang et al. [71] introduced an Occlusion Aware Warp Scheduler (OAWS) that focuses on TLP on memory resources. Their scheduler monitors and predicts memory resource usage, scheduling wavefronts that can be satisfied by the available memory resource. Both static and dynamic prediction methods were designed and implemented to predict the demand of MSHR entries of divergent memory instruction, maximizing the number of concurrent warps without memory occlusion. Based on their evaluation, OAWS can achieve up to a 73.1% performance gain compared to the GTO scheduler.

### **3.4 Improving Instruction Level Parallelism on GPUs**

Instead of reducing latency, several techniques focus on improving the overlap of compute and memory operations to exploit ILP on GPUs. Very Long Instruction Word (VLIW) instruction set architectures are designed to exploit ILP by encoding multiple independent operations in a single VLIW instruction. VLIW was adopted on AMD's Evergreen GPU architecture [4]. However, VLIW suffers from limited parallelism opportunities, as it solely relies on static analysis.

Gong et al. [15] proposed the Twin Kernel Multiple Thread (TKMT) execution model, which takes advantage of pursuing multiple instruction schedules in the compiler to improve the overlap of compute and memory operations. TKMT better distributes memory requests by reordering instructions for some wavefronts at compile time. This can significantly reduce the pressure on memory bandwidth, using the limited L1 cache more efficiently. TKMT can achieve a 12% average speedup over the baseline SIMT implementation model on various benchmarks on AMD Radeon GPUs.

Kim et al. [24] proposed a warped pre-execution approach on GPUs. In this technique,

wavefronts try to issue future instructions that are independent of the stalling instructions. Their method relies on hardware to dynamically detect such opportunities and may take several attempts before finding a proper candidate. In contrast to Kim et al.'s approach, we are leveraging static analysis at compile time, so our hinting approach is free from hardware dependency detection. In addition, guided by the information provided in hints, our approach can commit the correct program state more efficiently when wavefronts return to normal execution.

## **3.5** Improving GPU memory hierarchy utilization

Many researchers have proposed novel techniques to utilize the GPU cache and memory hierarchy more efficiently. Jog et al. [20] demonstrated that existing warp scheduling policies are unable to effectively incorporate data prefetching techniques due to scheduling consecutive warps. They proposed a prefetch-aware warp scheduling policy to schedule consecutive warps separately, which can work with a simple prefetcher nicely to tolerate memory latencies. They evaluated their design across a diverse set of applications and achieved a 25% speedup over a round-robin scheduler.

Rogers et al. proposed Divergence-aware warp scheduling (DAWS) [59], which introduces a divergence-based cache footprint predictor to maximize the utilization of intra-warp locality for the current active warps. The goal of DAWS is to keep the data that is reused by a warp maintained in cache so future accesses across loop iterations will result in a hit. According to their results, DAWS can achieve a 26% performance improvement over Cache Conscious Wavefront Scheduling [58].

Jog et al. [19] presented OWL, a CTA-aware scheduler that uses data locality information to limit the number of CTAs in each SM in order to reduce cache contention. OWL achieves these benefits by improving both the L1 cache hit rate and latency tolerance, improving DRAM bank parallelism and improving both DRAM row locality and cache hit rates.

MASCAR [63] introduces a bimodal warp scheduling scheme, along with a cache access re-execution system to increase overlap. Instead of distributing warps in a round-robin fashion, MASCAR prioritizes memory requests among warps when there is memory saturation detected to better overlap compute and memory instructions. Using the re-execution queue, they could better utilize cache locality and eliminate structural hazards when the memory subsystem becomes saturated. MASCAR achieves a 34% speedup over a baseline round-robin warp scheduler for memory intensive benchmarks.

Wang et al. [70] proposed a Divergence-Aware Cache (DaCache) management scheme that can orchestrate the warp scheduling policy and the L1 cache management together for GPUs. In DaCache, the insertion position in the cache of any incoming data block is decided by the current

warp's priority. Blocks of the warp with higher priority can enjoy a longer lifetime in cache. DaCache also prioritizes coherent loads over divergent loads durnig insertion, better utilizing intra-warp locality. Their experiments demonstrate that DaCache achieves a 40.4% performance improvement over the baseline GPU.

Oh et.al [52] proposed Adaptive Prefetching and Scheduling (APRES) to improve GPU cache efficiency. They demonstrated certain static load instructions in GPU applications have very high locality. Additionally, for some load instructions that have no locality, the addresses are heavily strided. APRES tries to group all the warps which execute the same load instruction within a short time and schedules them to utilize locality better. In addition, APRES tracks the inter-warp striding behavior and issues prefetches for different warps which execute the same load instructions. For memory intensive benchmarks, APRES can achieve a 31.7% performance improvement as compared to a baseline GPU model.

### **3.6 GPU Simulation Frameworks**

Given that a major contribution of this thesis is a GPU simulator, we will review prior GPU simulator efforts.

GPGPU-Sim [5] is a popular simulator that supports functional and cycle-level timing simulation based on the NVIDIA Fermi architecture. It has provided the GPU research community with important insights. It supports simulation on NVIDIA Parallel Thread Execution ISA (PTX) level. GPGPUSim also supports PTXPlus, which is an extended form of PTX, introduced in GPGPU-Sim 3.x. The developers claim it allows for a near one-to-one mapping of most GT200 (i.e., Fermi) SASS instructions to PTXPlus instructions. However, it only supports execution running at an intermediate language level and does not capture SASS execution.