# Electronics EECE2412 — Spring 2018 Exam #3

# Prof. Charles A. DiMarzio Department of Electrical and Computer Engineering Northeastern University

File:12262/exams/exam2

#### 20 April 2018

| Name: |  |  |  |

|-------|--|--|--|

|       |  |  |  |

#### General Rules:

- You may make use of three sheets of notes, 8.5-by-11 inches, using both sides of the page.

- You may use a calculator.

- Present your work as clearly as possible. I give partial credit if I can figure out that you know what you are doing. I do not give credit for putting down everything you know and hoping I will find something correct in it.

- Each question has a vertical black bar providing space for your work and a line for numerical answers or box for plots or drawings. Please write your answer to each question clearly. If it happens to be correct, I give you points quickly and move on to the next problem. Please show your work in the space provided, or on extra pages, clearly labeled with the problem number. If the answer is wrong, this will make it easy for me to find ways to give you partial credit.

- Avoid any appearance of academic dishonesty. Do not talk to other students during the exam. Keep phones, computers, and other electronic devices other than calculators secured and out of reach.

# 1 Short-Answer Questions

| 1. | Two MOSFETs have identical properties except that one has a larger channel width, $W$ . That one will have larger $K$ and will be capable of carrying more current. |

|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ,  | True  False                                                                                                                                                         |

| 2. | The gate current on an N–Channel MOSFET is                                                                                                                          |

|    | positive. negative. zero.                                                                                                                                           |

| 3. | Electrostatic precautions are more important working with BJTs than FETs.                                                                                           |

|    | True False                                                                                                                                                          |

| 4. | The threshold voltage $V_{t0}$ for an enhancement NFET is positive.                                                                                                 |

| •  | True False                                                                                                                                                          |

| 5. | Positive $V_{GS}$ on an N–Channel JFET will                                                                                                                         |

|    | increase the drain current. decrease the drain current destroy the transistor.                                                                                      |

| 6. | A common-drain amplifier is used for                                                                                                                                |

|    | unit voltage gain.  unit current gain.                                                                                                                              |

True

#### 2 FET DC Bias

#### Reading the Curves 2.1

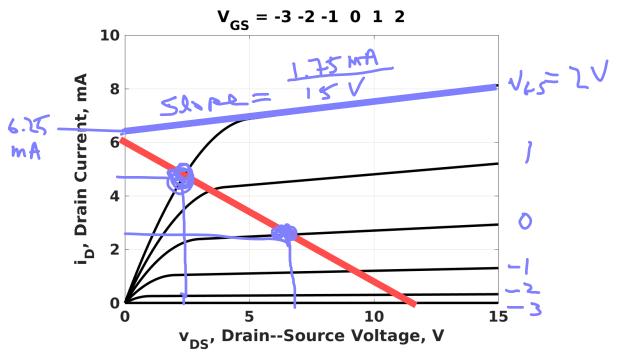

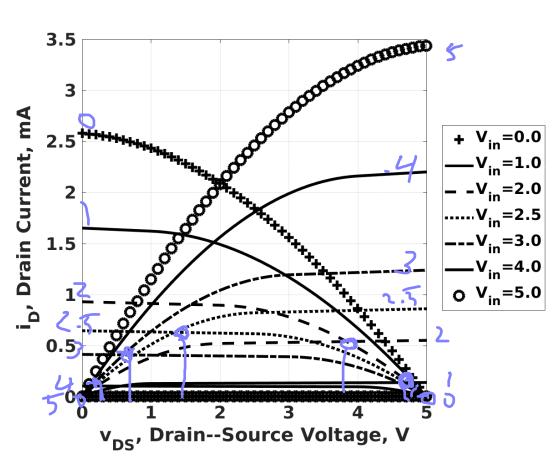

The figure shows a set of I–V curves for a particular NFET.

From the graph, determine the following (Assume  $kp = 50 \ \mu \text{A/V}^2$ );

Threshold Voltage,  $V_{t0} =$

Width/Length Ratio, W/L =

(actual wm 50) Approximate Early Voltage,  $V_A = \frac{54}{4}$

ID=6.25 WA

DiMarzio 12262/exams/exam2, Feb 2017

Page 4

#### 2.2 Load Line

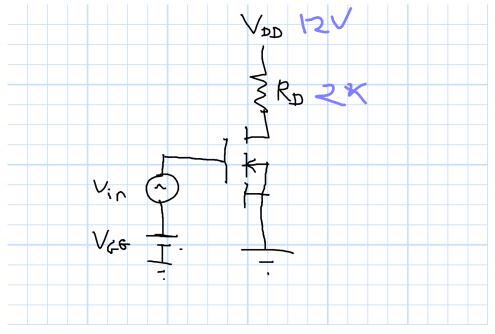

The transistor is placed in the following circuit.

For two cases, draw the load lines on the figure and write the equations for calculating the DC drain current,  $I_D$ . Remember that you can neglect the Early effect at this point.

You do not need to solve the equations; just write them and estimate the answer graphically from the plot.

Case 1:  $V_{GG} = 2 \text{ V}$

Equation: ZD=K(V66+3V)

Estimated Drain Current,  $I_D =$  mA.

Case 2:  $V_{GG} = 0 \text{ V}$

Equation:

Estimated Drain Current,  $I_D =$  mA

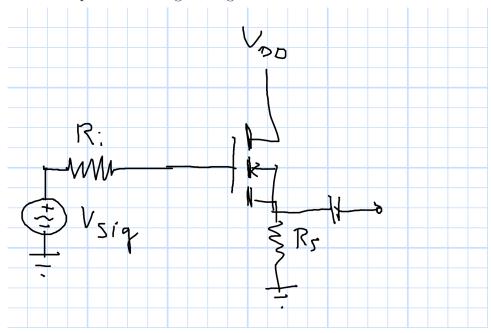

# 3 FET Amplifier

Consider the circuit shown. The transistor's Early voltage is  $V_A = 50$  V, and the transistor is in saturation. In the circuit, the transconductance is  $g_m = 2$  mA/V, the DC drain current is  $I_D = 2$  mA,  $R_i = 100$  k $\Omega$ ,  $R_S = 8$  k $\Omega$ , and the capacitor is "large enough."

## 3.1 Small Signal Parameters

What is W/L for this transistor? Remember  $kp = 50 \ \mu \text{A/V}^2$ .

$$W/L = 20$$

What is  $r_d$ ?

$$T_{d} = \frac{25 \text{ K}}{25 \text{ K}} \Omega.$$

$$T_{m} = \frac{25 \text{ K}}{25 \text{ K}} \Omega.$$

Draw the AC circuit.

# 3.2 Amplifier Parameters

What is the voltage gain?

$$A_V = \frac{9}{2}$$

What is the input impedance?

$$Z_{in} =$$

Ohms.

What is the output impedance?

$$Z_{out} =$$

Ohms.

### 3.3 Bonus Question

You do not need to answer this to score 100 on the exam. If you answer it correctly, I'll use the points in some way that will help your course grade.

What is the minimum voltage for  $V_{DD}$  to make this circuit work?

$$V_{DD} = \frac{1}{2} \times \frac{1}{$$

#### FET Logic 4

#### **Transfer Function** 4.1

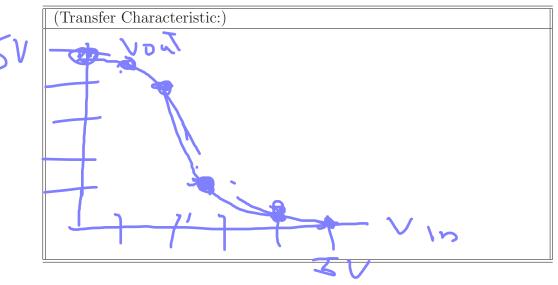

From the given transistor curves for a CMOS logic inverter in the figure above, draw the transfer function. Be sure to show numbers on the axes.

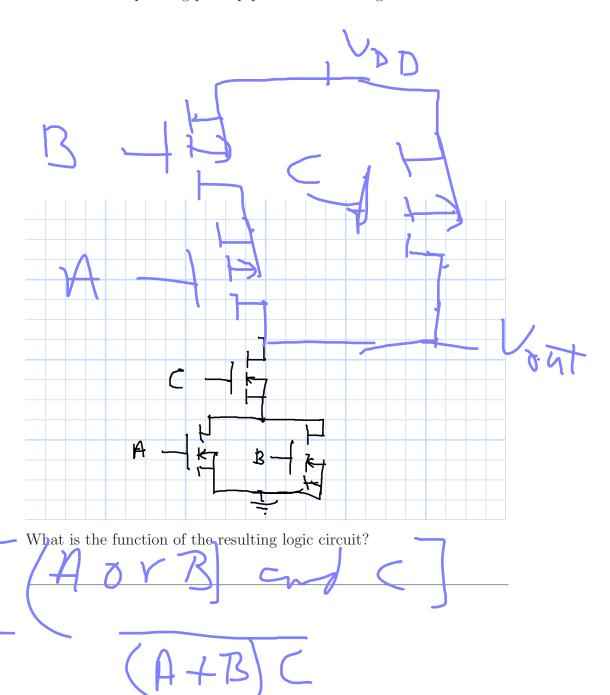

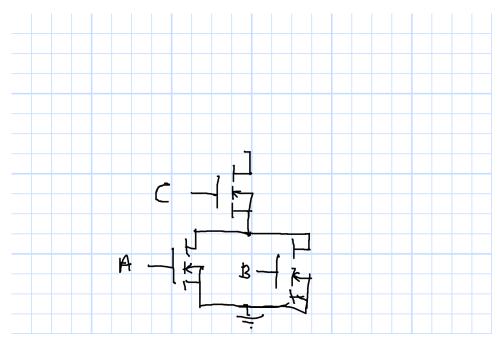

The figure shows the pull–down portion of a logic gate with three inputs. For all possible combinations of true and false inputs, show show whether the pull–down circuit is open or shorted.

| A | В | С | Open or Short? |

|---|---|---|----------------|

| 0 | 0 | 0 | ORen           |

| 0 | 0 | 1 | ora            |

| 0 | 1 | 0 | ORA            |

| 0 | 1 | 1 | لماد           |

| 1 | 0 | 0 | 3 pm           |

| 1 | 0 | 1 | 5 lut          |

| 1 | 1 | 0 | Opm            |

| 1 | 1 | 1 | sint           |

Draw the corresponding pull-up portion on the diagram below.