Contents

idtarget=125e-6;

vddtarget=12;

Transistor parameters

kp=50e-6;w=10e-6;l=2e-6;vt0=4;

vdaxis=0:0.1:vddtarget;

vgaxis=[0:0.25:1.5]+vt0;

[vd,vg]=meshgrid(vdaxis,vgaxis);

const=kp*w/l

const =

2.5000e-04

Current calculation

idsat=const*(vg-vt0).^2/2;

idtriode=const*((vg-vt0).*vd-vd.^2/2);

idboundary=const*vd.^2/2;

id=idtriode.*(idtriode>=idboundary)+idsat.*(idsat<idboundary);

We set vg to vd, so we can plot id against vd

idshortgd=const*(vd-vt0).^2/2.*(vd>=vt0);

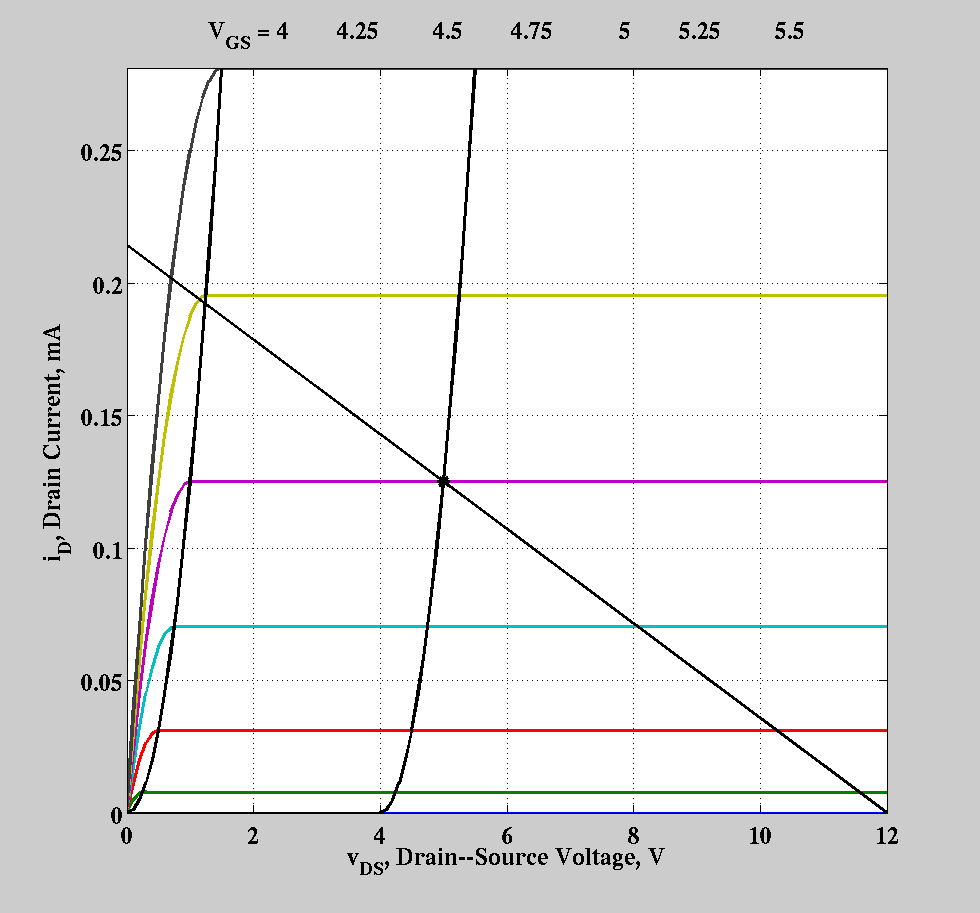

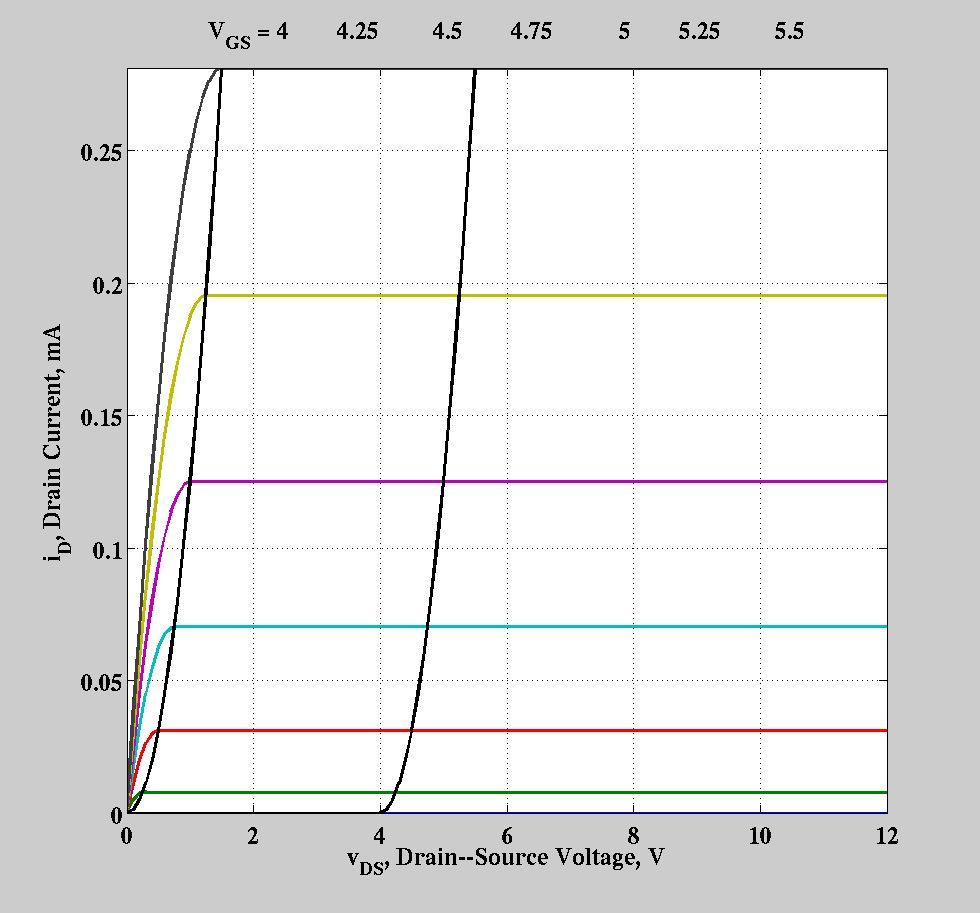

Plot the transistor curves

figure;plot(vdaxis,id*1e3);hold on;

plot(vdaxis,idboundary*1e3,'k');

plot(vdaxis,idshortgd*1e3,'k');grid on;

hold off;

title(['V_{GS} = ',num2str(vgaxis)]);

xlabel('v_{DS}, Drain--Source Voltage, V');

ylabel('i_{D}, Drain Current, mA');

axis([0,max(vdaxis),0,max(max(id))*1e3]);

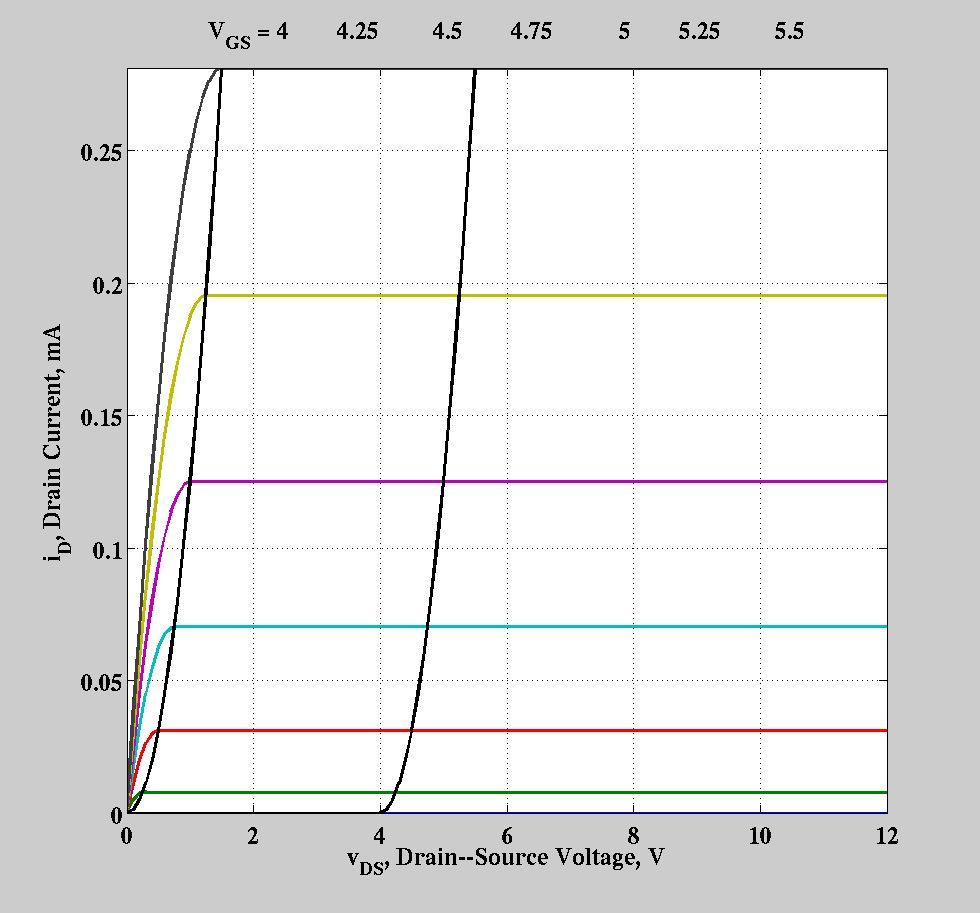

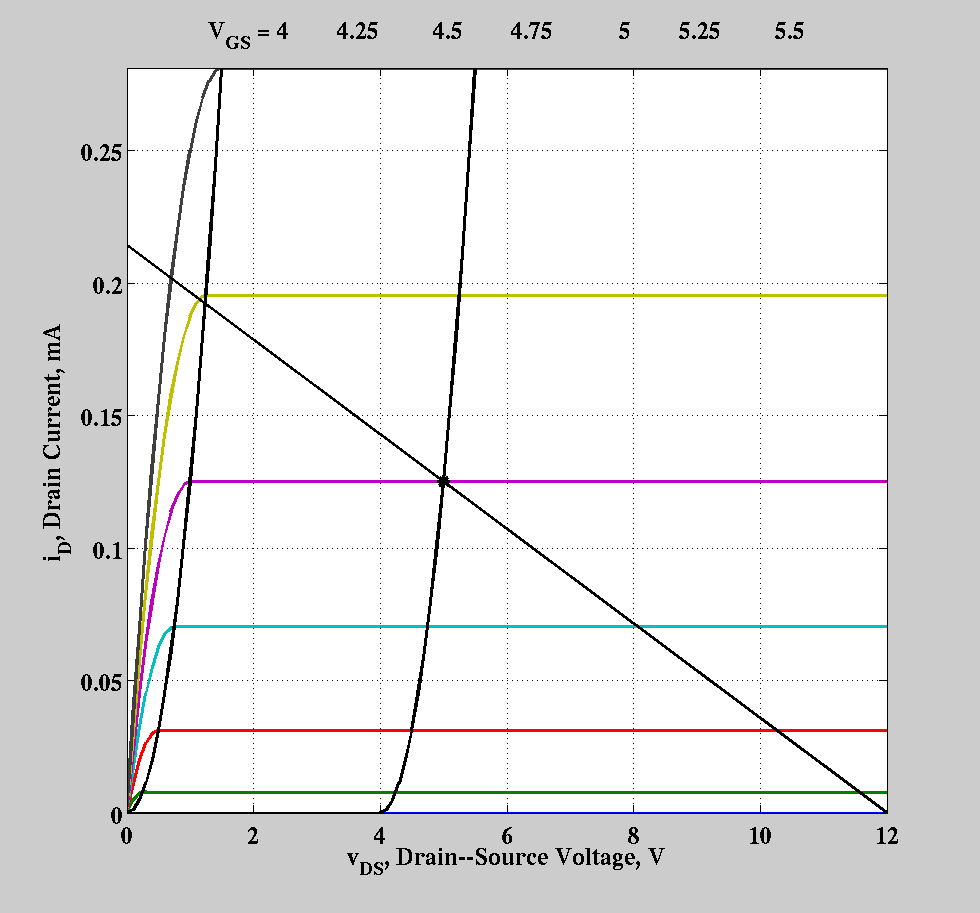

Find the Q point for the target current

vgQ=vt0+sqrt(2*idtarget/const)

vgQ =

5

Try to find a resistor

vdQ=vgQ;

r=(vddtarget-vdQ)/idtarget

r =

56000

Plot everyting

figure;plot(vdaxis,id*1e3);hold on;

plot(vdaxis,idboundary*1e3,'k');

plot(vdaxis,idshortgd*1e3,'k');

plot(vdQ,idtarget*1e3,'k*');

plot([0,vddtarget],[vddtarget/r,0]*1e3,'k');grid on;

hold off;

title(['V_{GS} = ',num2str(vgaxis)]);

xlabel('v_{DS}, Drain--Source Voltage, V');

ylabel('i_{D}, Drain Current, mA');

axis([0,max(vdaxis),0,max(max(id))*1e3]);